## COMPUTER-AIDED SYNTHESIS AND VERIFICATION OF GATE-LEVEL TIMED CIRCUITS

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> By Christopher John Myers October 1995

© Copyright 1995 by Christopher John Myers I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

> Teresa H.-Y. Meng (Principal Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

David L. Dill

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Adam P. Arkin

Approved for the University Committee on Graduate Studies:

Dean of Graduate Studies & Research

# Abstract

In recent years, there has been a resurgence of interest in the design of *asynchronous circuits* due to their ability to eliminate clock skew problems, achieve average case performance, adapt to processing and environmental variations, provide component modularity, and lower system power requirements. Traditional academic asynchronous designs methods use unbounded delay assumptions, resulting in circuits that are verifiable, but ignore timing for simplicity, leading to unnecessarily conservative designs. In industry, however, timing is critical to reduce both chip area and circuit delay. Due to a lack of formal methods that handle timing information correctly, circuits with timing constraints usually require extensive simulation to gain confidence in the design.

This thesis bridges this gap by introducing *timed circuits* in which explicit timing information is incorporated into the specification and utilized throughout the design procedure to optimize the implementation. Our timed circuits are more efficient than those produced using untimed methods and more reliable than those produced using *ad hoc* design techniques. Timing analysis, however, often introduces substantial complexity into the design procedure, and has hitherto either been avoided, simplified, or considered only after synthesis. In this thesis, we describe an exact and efficient timing analysis algorithm, and its application to the automatic synthesis and verification of gate-level timed circuits. Our synthesis procedure generates hazard-free timed circuits and maps the resulting implementations to practical, semi-custom gate libraries. The resulting implementations are up to 40 percent smaller and 50 percent faster than previous asynchronous designs. We also demonstrate that our timed designs can be smaller and faster than their synchronous counterparts. After back-annotating the synthesized circuits, our verification procedure checks that all circuits satisfy their specifications. This procedure has also been applied to a wide collection of highly concurrent timed circuits that could not previously be verified.

# Acknowledgments

I am indebted to my adviser, Professor Teresa Meng, for suggesting this research topic to me and giving me support and patience as I struggled with it. Professor David Dill, my associate adviser, provided substantial technical support, and I would like to thank him for many very enlightening discussions about timed circuits and many other matters. I am grateful to Dr. Adam Arkin for serving as my third reader and showing me a wider scope of application for my research. Professor Giovanni DeMicheli is also gratefully acknowledged for his advice on my work. Finally, I would like to thank Professor Greg Kovacs and Professor Kunle Olukotun for serving on my orals committee.

I have been very fortunate in my years at Caltech and Stanford to get the opportunity to work with many brilliant people. I would like to thank Alain Martin for introducing me to the world of asynchronous design. Peter Beerel has been my colleague, officemate, and friend since I arrived at Stanford. I greatly appreciate his comments and criticizisms which significantly improved the quality of this work. In particular, his collaboration on the synthesis and technology mapping chapters is gratefully acknowledged. I was also very fortunate to be able to collaborate with Tom Rokicki on the timing analysis and verification chapters. I'm indebted to him for helping me deal with a world filled with choices. I would also like to thank all the past members of the Stanford asynchronous group (Jerry Burch, Bill Coates, Al Davis, Jeremy Gunawardena, Steve Nowick, Polly Siegel, and Ken Yun) for providing a stimulating working environment. Finally, I would like to thank Steve Burns and Gaetano Borriello for their advice and support through the years.

Numerous individuals provided invaluable moral support. In particular, I would like to thank Janet Lai for her friendship. I'm grateful to Lilian Betters for her administrative help throughout the years, especially during my job search. I would also like to thank the many other friends who gave me wonderful distractions from work (Francis Chong, Korhan Gurkan, Jeff Jones, Joe Lauer, John Lazzaro, Garland Lee, Jared Levy, Amit Mehra, Misha Samoilov, Craig Sosin, Emily Wen, and Su-lin Wu), the other members of Teresa's group (Navin Chaddha, Ben Gordon, Andy Hung, Won Namgoong, Clem Portmann, Wee-chiew Tan, Tony Todesco, and Ely Tsern), and my parents and family for their encouragement and support.

This work was supported by an NSF fellowship, the Semiconductor Research Corporation contract 93-DJ-205, a grant from the NSF PYI Program, the Office of Navel Research contract N00014-89-J-3036, and the Advanced Research Projects Agency contract DABT63-91-K-0002. Finally, much of this thesis was reworked at Intel in Israel during the summer of 1995 while consulting with Shai Rotem whom I am grateful to for allowing me the opportunity to apply my work.

# Contents

| 1 | Intr | oducti  | on                                                     | 1  |

|---|------|---------|--------------------------------------------------------|----|

|   | 1.1  | Asynch  | nronous Circuit Design                                 | 2  |

|   |      | 1.1.1   | Delay-Insensitive Circuits                             | 4  |

|   |      | 1.1.2   | Quasi-Delay Insensitive and Speed-Independent Circuits | 5  |

|   |      | 1.1.3   | Fundamental-Mode Circuits                              | 5  |

|   |      | 1.1.4   | Timed Circuits                                         | 6  |

|   | 1.2  | Contri  | butions                                                | 7  |

|   | 1.3  | Thesis  | Overview                                               | 8  |

| 2 | Tim  | ed Spe  | ecifications                                           | 10 |

|   | 2.1  | Timed   | Handshaking Expansions                                 | 10 |

|   |      | 2.1.1   | Modules, Signal Declarations, and Processes            | 11 |

|   |      | 2.1.2   | Basic Commands and Their Composition                   | 12 |

|   |      | 2.1.3   | Guarded Commands                                       | 12 |

|   |      | 2.1.4   | Example                                                | 14 |

|   | 2.2  | Timed   | Event-Rule Structures                                  | 18 |

|   | 2.3  | Timed   | Configurations                                         | 19 |

|   | 2.4  | Interpr | eting the Specification Language                       | 21 |

|   |      | 2.4.1   | Declarations                                           | 21 |

|   |      | 2.4.2   | Composition of Timed Event-Rule Structures             | 22 |

|   |      | 2.4.3   | Renaming of Timed Event-Rule Structures                | 23 |

|   |      | 2.4.4   | Interpretation of a Non-Repetitive Process             | 23 |

|   |      | 2.4.5   | Interpretation of a Repetitive Process                 | 25 |

|   |      | 2.4.6   | Vacuous Events                                         | 26 |

|   |      | 2.4.7   | Interpretation of a Module                             | 26 |

|   |     | 2.4.8  | Example                                                                |

|---|-----|--------|------------------------------------------------------------------------|

| 3 | Tin | ning A | nalysis 32                                                             |

|   | 3.1 | Const  | raint graphs                                                           |

|   | 3.2 | Estim  | ating the Worst-Case Time Difference                                   |

|   |     | 3.2.1  | Worst-Case Time Difference                                             |

|   |     | 3.2.2  | Algorithm to Estimate the Worst-Case Time Difference                   |

|   |     | 3.2.3  | Proof of Correctness 39                                                |

|   |     | 3.2.4  | Complexity of the Algorithm 40                                         |

|   |     | 3.2.5  | Extensions to Find a Better Estimate 40                                |

|   |     | 3.2.6  | Termination of the Algorithm                                           |

|   |     | 3.2.7  | Removing Redundant Rules                                               |

|   | 3.3 | Orbita | al Nets                                                                |

|   |     | 3.3.1  | Timing Requirements   43                                               |

|   |     | 3.3.2  | Simultaneous Actions                                                   |

|   |     | 3.3.3  | Operational Semantics                                                  |

|   |     | 3.3.4  | Transformation from a Timed ER Structure to an Orbital Net $\ldots$ 47 |

|   |     | 3.3.5  | Satisfying the Single Behavior Place Requirement                       |

|   | 3.4 | Partia | l Order Timing                                                         |

|   |     | 3.4.1  | Geometric Regions                                                      |

|   |     | 3.4.2  | State Space Exploration with Geometric Timing                          |

|   |     | 3.4.3  | Performance of Geometric Timing                                        |

|   |     | 3.4.4  | Concurrency, Causality, and Posets                                     |

|   |     | 3.4.5  | State Space Exploration with Partial Order Timing                      |

|   |     | 3.4.6  | Efficiency Considerations                                              |

|   | 3.5 | Findir | ng the Reduced State Graph 58                                          |

| 4 | Syn | thesis | 65                                                                     |

|   | 4.1 | Sum-c  | of-Products Implementation                                             |

|   | 4.2 | Gener  | alized C-Implementation                                                |

|   | 4.3 |        | ard C-Implementation                                                   |

|   |     | 4.3.1  | Excitation Regions and Quiescent States                                |

|   |     | 4.3.2  | Correct Covers                                                         |

|   | 4.4 | Findir | ng Enabled Cubes and Trigger Cubes                                     |

|   | 4.5            | Finding an Optimal Correct Cover               |

|---|----------------|------------------------------------------------|

|   | 4.6            | Synthesis Results                              |

| 5 | Tec            | hnology Mapping 80                             |

|   | 5.1            | Gate Libraries                                 |

|   | 5.2            | Decomposition                                  |

|   |                | 5.2.1 Searching the Decomposition Space        |

|   |                | 5.2.2 Decomposition Through Resynthesis        |

|   |                | 5.2.3 Multi-level Decompositions               |

|   | 5.3            | Example                                        |

|   | 5.4            | Technology Mapping Results                     |

| 6 | $\mathbf{Des}$ | ign Examples 94                                |

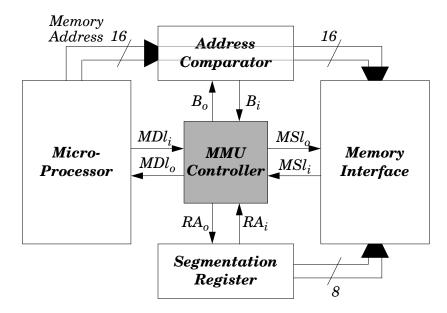

|   | 6.1            | MMU Controller                                 |

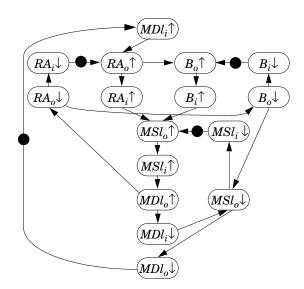

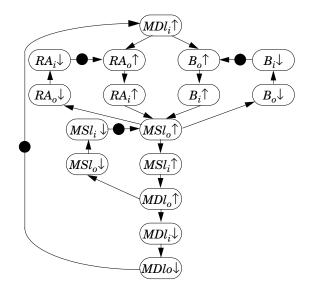

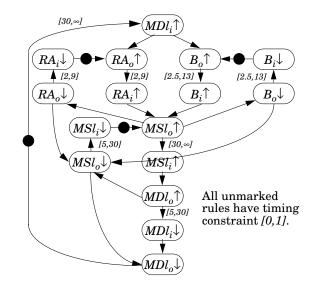

|   |                | 6.1.1 The Memory Data Load Cycle               |

|   |                | 6.1.2 Complete MMU                             |

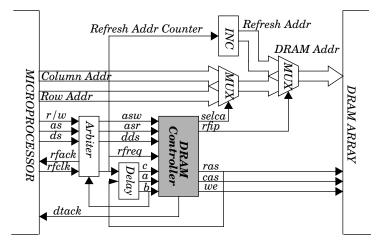

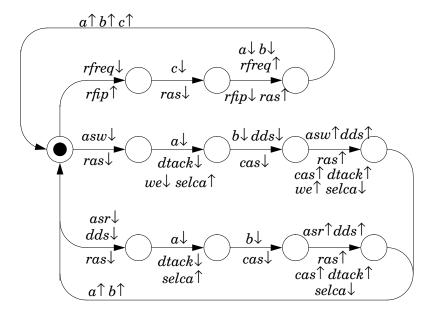

|   | 6.2            | DRAM Controller                                |

|   | 6.3            | Two-bit Synchronous Counter                    |

| 7 | Ver            | ification 109                                  |

|   | 7.1            | Behavioral Semantics                           |

|   | 7.2            | Generating the Orbital Net Representations     |

|   | 7.3            | Reporting Failures                             |

|   | 7.4            | Verification Results                           |

| 8 | Cor            | nclusions 116                                  |

|   | 8.1            | Summary                                        |

|   | 8.2            | Future Work                                    |

|   |                | 8.2.1 Specification                            |

|   |                | 8.2.2 Compilation                              |

|   |                | 8.2.3 Technology Mapping and Module Generation |

|   |                | 8.2.4 Verification                             |

|   |                | 8.2.5 Asynchronous Datapaths 119               |

|   |                | 8.2.6 Interfacing with Synchronous Designs 119 |

# List of Tables

| 1 | Enabled cubes and trigger cubes for the SEL                                            | 72  |

|---|----------------------------------------------------------------------------------------|-----|

| 2 | CC table for $(out 2_o \downarrow, 0)$ from the SEL                                    | 74  |

| 3 | CC table for $(out 2_o \downarrow, 0)$ from the SEL after removing dominating columns. | 75  |

| 4 | Synthesis results                                                                      | 77  |

| 5 | Technology mapping results                                                             | 92  |

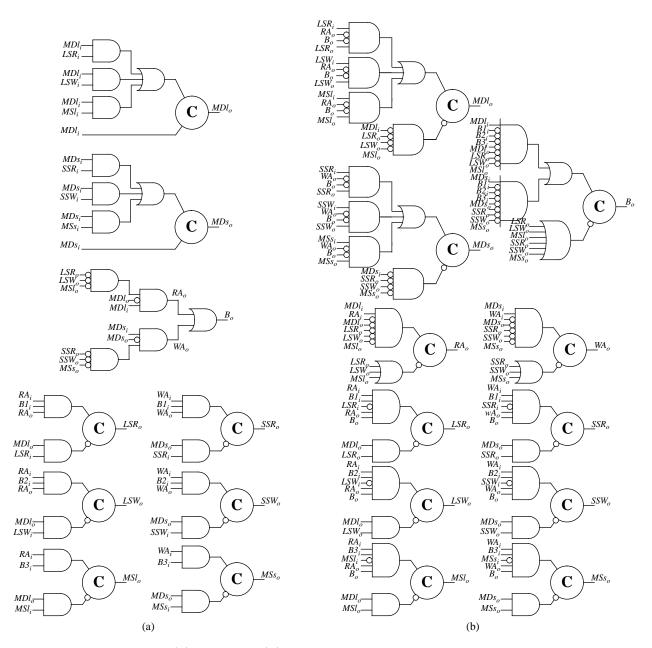

| 6 | Production rules for speed-independent and timed circuits for the MDl cycle.           | 98  |

| 7 | Verification results                                                                   | 114 |

# List of Figures

| 1  | Modules, signal declarations, and processes                                                               | 12 |

|----|-----------------------------------------------------------------------------------------------------------|----|

| 2  | Basic commands and their composition                                                                      | 12 |

| 3  | Guarded commands                                                                                          | 13 |

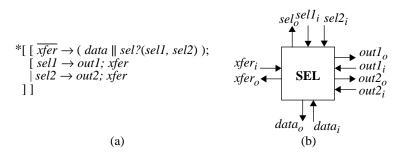

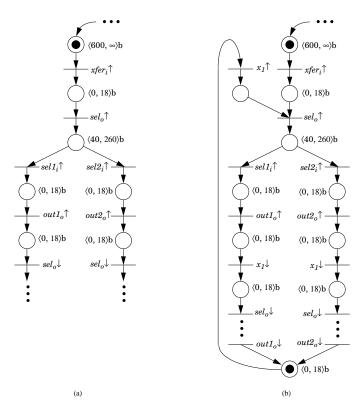

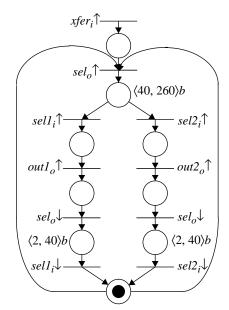

| 4  | (a) CSP specification and (b) block diagram for a port selector (SEL)                                     | 14 |

| 5  | Part of the timed HSE specification for the SEL                                                           | 17 |

| 6  | Reshuffling of the <i>selctrl</i> process.                                                                | 17 |

| 7  | Complete BNF description for the timed HSE specification language                                         | 29 |

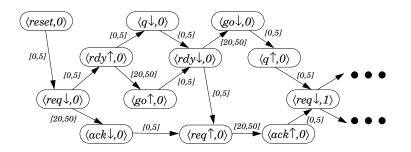

| 8  | Part of the timed HSE specification for the SEL                                                           | 30 |

| 9  | Format for a timed ER structure                                                                           | 30 |

| 10 | Timed ER structure for the <i>sel</i> process from the SEL                                                | 31 |

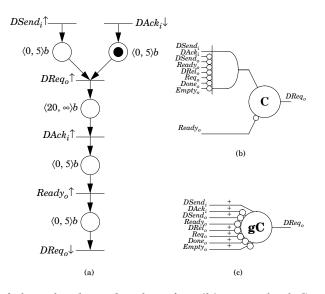

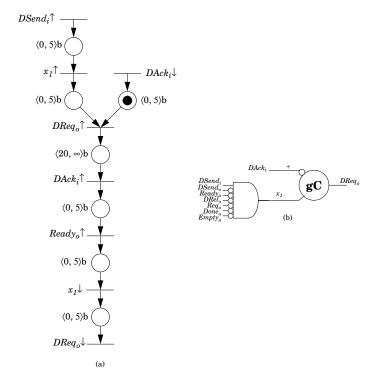

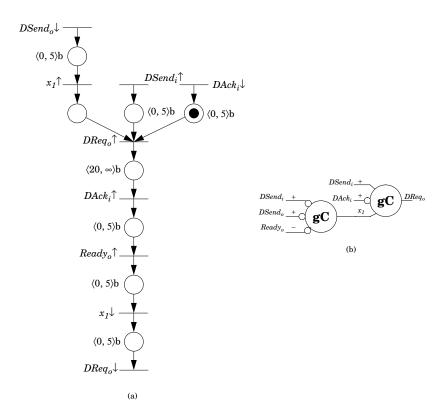

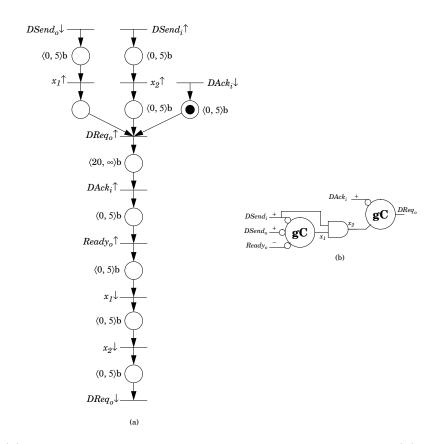

| 11 | Timed HSE specification for a SCSI protocol controller                                                    | 34 |

| 12 | Cyclic constraint graph for a SCSI protocol controller                                                    | 34 |

| 13 | Part of the acyclic constraint graph for the SCSI protocol controller                                     | 35 |

| 14 | Algorithm to find an estimate of the worst-case time difference in a cyclic                               |    |

|    | graph                                                                                                     | 38 |

| 15 | Algorithm to find a time difference in an acyclic graph                                                   | 38 |

| 16 | Algorithm to find a maximum time difference in an acyclic graph. $\ldots$ .                               | 39 |

| 17 | Algorithm to find redundant rules                                                                         | 42 |

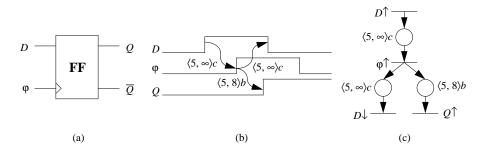

| 18 | (a)A D-type flip-flop; (b) its timing requirements represented using a timing                             |    |

|    | diagram; (c) its timing requirements represented using an orbital net. $\ldots$                           | 44 |

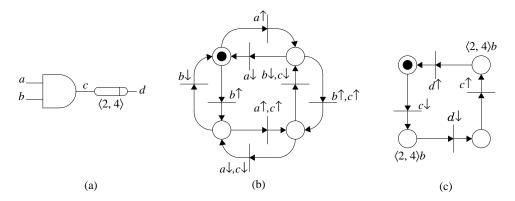

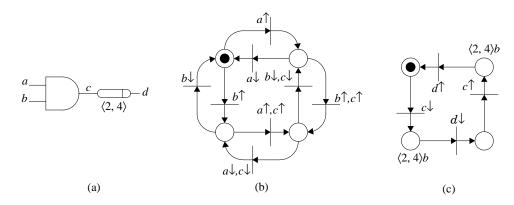

| 19 | (a) AND gate with inputs $a$ and $b$ , and output $d$ ; (b) orbital net for its                           |    |

|    | functional behavior; (c) delay buffer with input $c$ , output $d$ , and delay of $\langle 2, 4 \rangle$ . | 46 |

| 20 | Algorithm to transform a timed ER structure to an orbital net                                             | 49 |

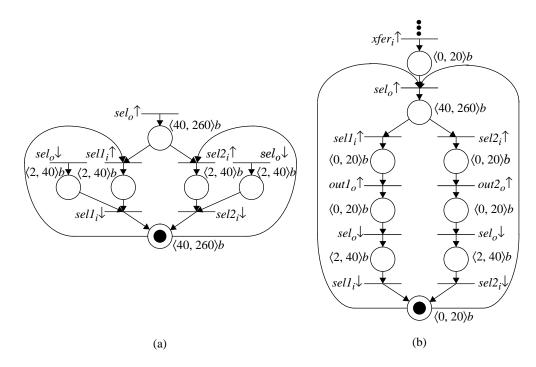

| 21 | (a) Orbital net for the <i>sel</i> process from the SEL; (b) part of the orbital net                      |    |

|    | after composition with the other processes.                                                               | 50 |

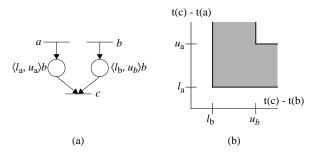

| 22 | (a) Fragment of the orbital net that violates the single behavior place re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | quirement; (b) graphical representation of the desired timing behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51 |

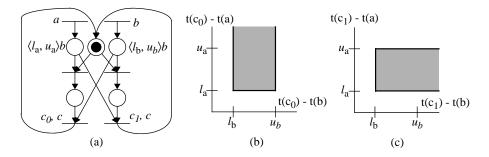

| 23 | (a) Orbital net that satisfies the single behavior place requirement; graphical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|    | representation of the timing behavior of $c_0$ (b) and $c_1$ (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

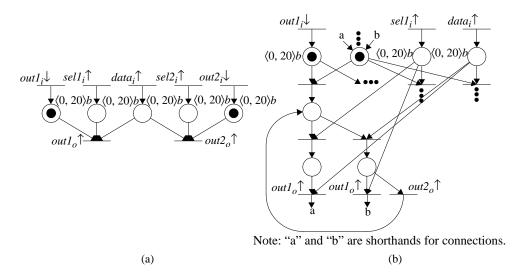

| 24 | (a) Fragment of an orbital net with a behavior place that has multiple tran-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|    | sitions in its postset; (b) part of the transformed orbital net that satisfies the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|    | single behavior place requirement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51 |

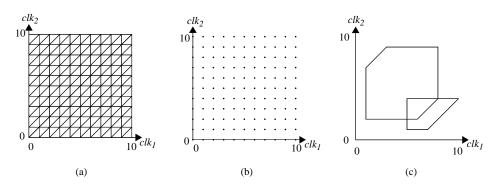

| 25 | (a) Unit-cube, (b) discrete, and (c) geometric representations of the timed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|    | state space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52 |

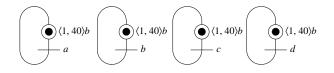

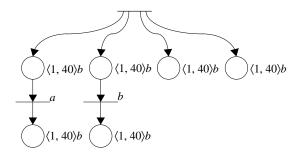

| 26 | The adverse example adv4x40 with $n = 4$ and $k = 40$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 |

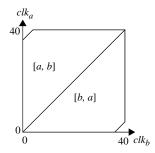

| 27 | Geometric regions from the adverse example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56 |

| 28 | One poset from the adverse example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56 |

| 29 | Algorithm to find the reduced state graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60 |

| 30 | Algorithm to check if an event is slow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61 |

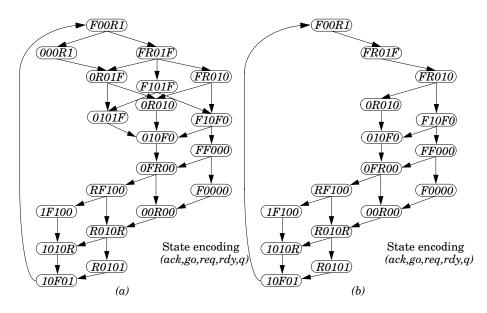

| 31 | (a) SG and (b) RSG for the SCSI protocol controller. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62 |

| 32 | Redundant rules from the SCSI protocol controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63 |

| 33 | Reduced state graph for the SCSI protocol controller. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64 |

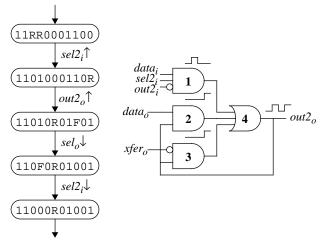

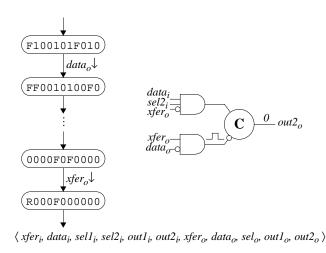

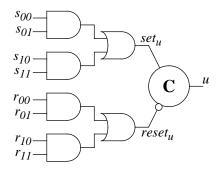

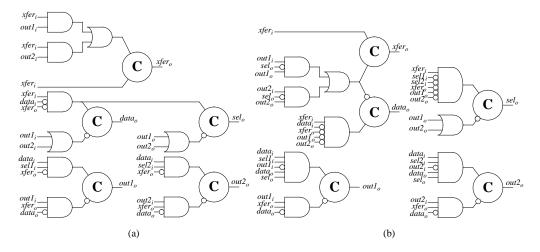

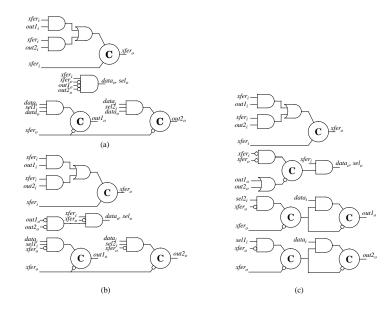

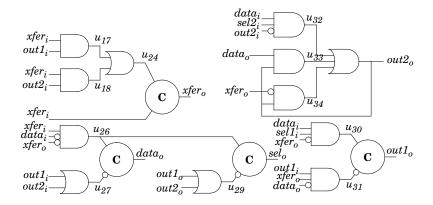

| 34 | A hazardous sum-of-products implementation of $\mathit{out2_o}$ from the SEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67 |

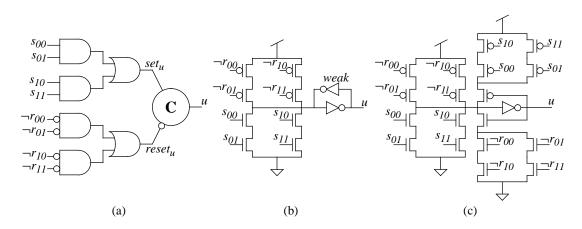

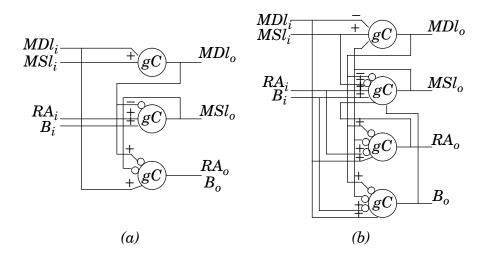

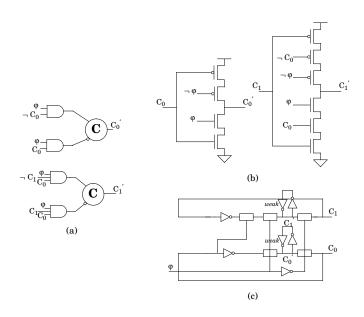

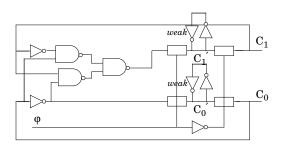

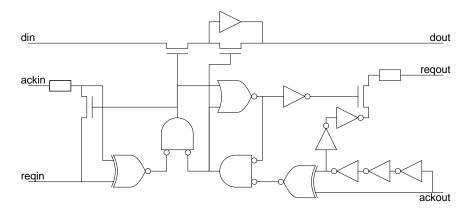

| 35 | (a) The generalized C-element configuration with (b) weak-feedback and (c) $\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    | fully-static CMOS implementations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68 |

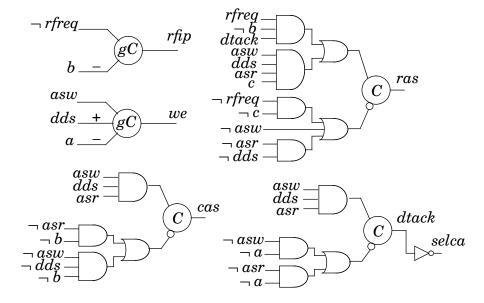

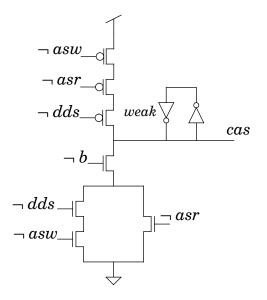

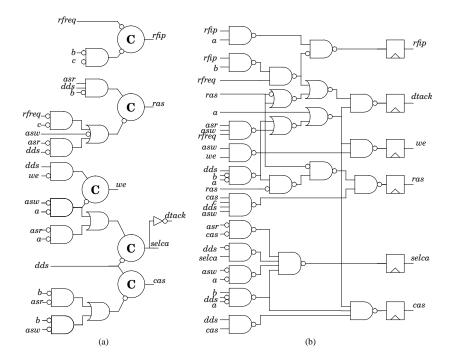

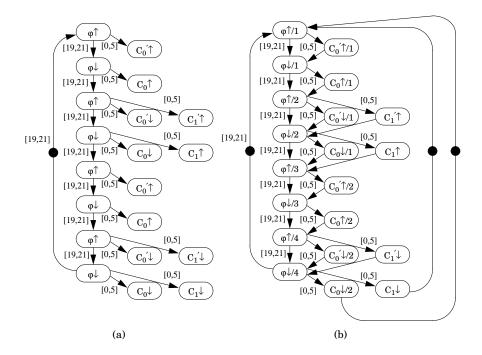

| 36 | A hazardous gate-level implementation of $out2_o$ from the SEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68 |