$See \ discussions, stats, and \ author \ profiles \ for \ this \ publication \ at: \ https://www.researchgate.net/publication/2786211$

# Architectural-Level Synthesis Of Asynchronous Systems

Article · April 1999

Source: CiteSeer

CITATIONS 6 3 authors, including: Erik Brunvand University of Utah 117 PUBLICATIONS 1,342 CITATIONS SEE PROFILE reads 68

# ARCHITECTURAL-LEVEL SYNTHESIS OF ASYNCHRONOUS SYSTEMS

by

Brandon M. Bachman

A thesis submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical Engineering

The University of Utah

December 1998

Copyright © Brandon M. Bachman 1998

All Rights Reserved

### THE UNIVERSITY OF UTAH GRADUATE SCHOOL

## SUPERVISORY COMMITTEE APPROVAL

of a thesis submitted by

Brandon M. Bachman

This thesis has been read by each member of the following supervisory committee and by majority vote has been found to be satisfactory.

Chair: Chris J. Myers

Erik Brunvand

Christian Schlegel

### THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# FINAL READING APPROVAL

To the Graduate Council of the University of Utah:

I have read the thesis of <u>Brandon M. Bachman</u> in its final form and have found that (1) its format, citations, and bibliographic style are consistent and acceptable; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the Supervisory Committee and is ready for submission to The Graduate School.

Date

Chris J. Myers Chair, Supervisory Committee

Approved for the Major Department

Om P. Gandhi Chair/Dean

Approved for the Graduate Council

David S. Chapman Dean of The Graduate School

## ABSTRACT

Asynchronous circuit design has the potential to produce circuits superior to those of synchronous circuit design. Current synchronous methods of architectural-level synthesis do not exploit properties inherent to asynchronous circuits. This research describes potential optimizations and techniques that can be applied to the architectural-level design of asynchronous systems. The proposed methods take advantage of asynchronous circuit properties such as data-dependent delays, modularity, and composibility. The optimization problems of scheduling and allocation are studied. For scheduling, some counterintuitive properties of delays in a system are shown. The design space is studied and several filters to reduce the size of the design space are proposed. To evaluate and test these ideas the CAD tool Mercury was developed and is described in detail. Mercury is unique in that it can take an abstract model of a design, in this case a data flow graph, and from that generate both an optimal structural view of an asynchronous datapath for the design, as well as the necessary behavioral control to operate that datapath. Several case studies are presented utilizing the tool and methods to illustrate the practical aspects of this work.

To my loving wife, Marianne, and to my parents, Danel and Patricia.

## CONTENTS

| AB             | STRACT                                     | iv            |

|----------------|--------------------------------------------|---------------|

| LIS            | T OF FIGURES                               | viii          |

| $\mathbf{LIS}$ | T OF TABLES                                | x             |

| AC             | KNOWLEDGEMENTS                             | xi            |

| СН             | APTERS                                     |               |

| 1.             | INTRODUCTION                               | 1             |

|                |                                            |               |

|                |                                            | $\frac{2}{3}$ |

|                | 1.2 Related Work                           | 3<br>5        |

|                | 1.3 Contributions       1.4 Thesis Outline | 5<br>6        |

|                |                                            | 0             |

| 2.             | ARCHITECTURAL LEVEL MODELING               | 8             |

|                | 2.1 Representation and Modeling            | 8             |

|                | 2.2 Modeling Resources                     | 12            |

|                | 2.3 System Constraints                     | 15            |

|                | 2.4 Output                                 | 16            |

|                | 2.4.1 Datapath Generation                  | 16            |

|                | 2.4.2 Control Generation                   | 20            |

| 3.             | DESIGN SPACE EXPLORATION                   | 25            |

|                | 3.1 Binding                                | 26            |

|                | 3.2 Scheduling                             | 26            |

|                | 3.2.1 ASAP Scheduling                      | 27            |

|                | 3.2.2 ALAP Scheduling                      | 28            |

|                | 3.2.3 Mobility                             | 29            |

|                | 3.2.4 Force-Directed Scheduling            | 30            |

|                | 3.2.5 Statistical Delay Calculation        | 31            |

|                | 3.2.6 Monte-Carlo Delay Calculation        | 32            |

|                | 3.3 Typical Delay                          | 33            |

|                | 3.4 Resource Allocation                    | 34            |

|                | 3.4.1 Left-Edge Algorithm                  | 36            |

|                | 3.4.2 Clique Covering                      | 39            |

| 4.             | THE DESIGN SPACE                           | 41            |

|                | 4.1 Reducing the Design Space              | 42            |

|                | 4.2 Filters                                | 43            |

|                | 4.2.1 Infeasible Edges                     | 43            |

|    | 4.2.2         Redundancy                   | $44 \\ 46$ |

|----|--------------------------------------------|------------|

|    | 4.2.4 Minimal Latency                      | 47         |

|    | 4.2.5 Constraints                          | 48         |

|    | 4.2.6 Maximally Shared Resources           | 48         |

|    | 4.2.7 No Change In Objectives              | 49         |

|    | 4.3 Hierarchal Exploration                 | 49         |

| 5  | . SYSTEM IMPLEMENTATION                    | 52         |

|    | 5.1 General Algorithm                      | 52         |

|    | 5.2 Optimizations                          | 55         |

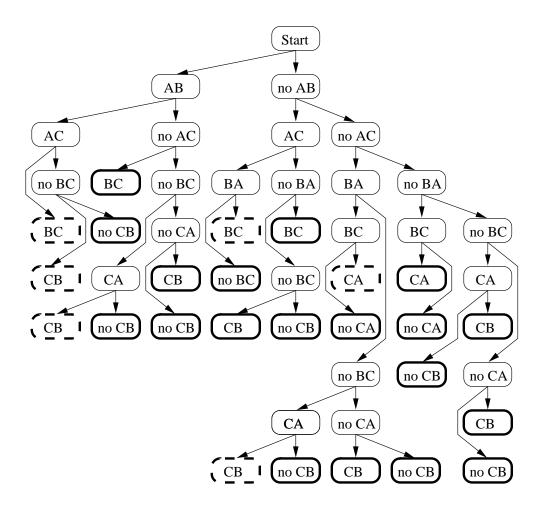

|    | 5.2.1 Dynamic Transitive Closure           | 56         |

|    | 5.2.2 Dynamic Scheduling                   | 57         |

| 6  | . CASE STUDIES                             | 60         |

|    | 6.1 Differential Equation Solver           | 60         |

|    | 6.2 Elliptical Wave Filter                 | 65         |

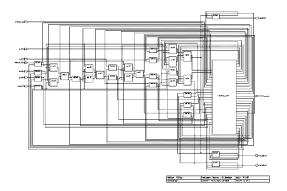

|    | 6.2.1 Comparison with Synchronous Methods. | 69         |

|    | 6.3 Inverse Discrete Cosine Transform      | 70         |

| 7. | . CONCLUSIONS                              | 75         |

|    | 7.1 Possible Extensions                    | 76         |

| Α  | PPENDICES                                  |            |

| Α  | SAMPLE VHDL DATAPATH                       | 79         |

| в  | <b>SAMPLE VHDL CONTROL</b>                 | 82         |

|    |                                            |            |

| С  | 2. SAMPLE VHDL CONFIGURATION               | 85         |

|    |                                            |            |

## LIST OF FIGURES

| 1.1  | Mercury design flow.                                                    | 7  |

|------|-------------------------------------------------------------------------|----|

| 2.1  | Behavioral VHDL and corresponding data flow graph                       | 10 |

| 2.2  | Input format for a data flow graph (DFG)                                | 11 |

| 2.3  | Sample data flow graph and model description.                           | 12 |

| 2.4  | Request/acknowledge interface with four-phase handshake protocol        | 13 |

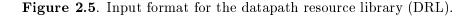

| 2.5  | Input format for the datapath resource library (DRL)                    | 14 |

| 2.6  | Sample datapath resource library (DRL)                                  | 15 |

| 2.7  | Input format for constraints.                                           | 15 |

| 2.8  | Sample constraints specification.                                       | 16 |

| 2.9  | Datapath format                                                         | 17 |

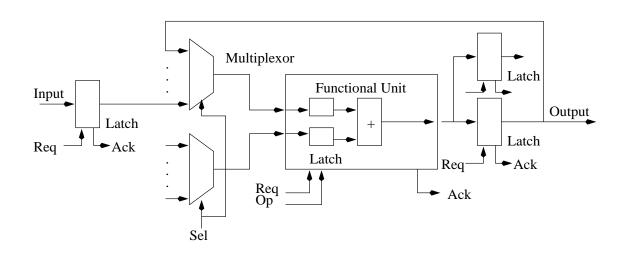

| 2.10 | Datapath generated from sample model description                        | 18 |

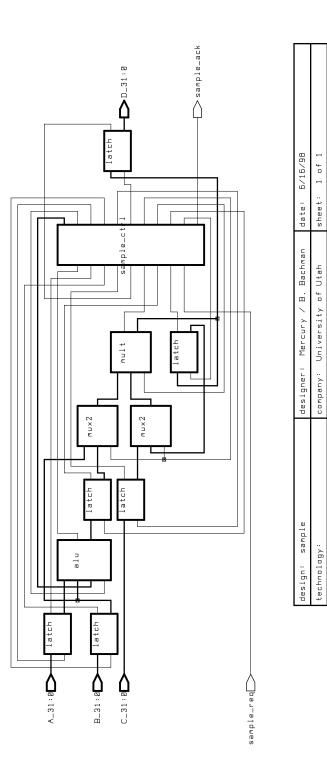

| 2.11 | Timing diagram showing handshaking protocol                             | 23 |

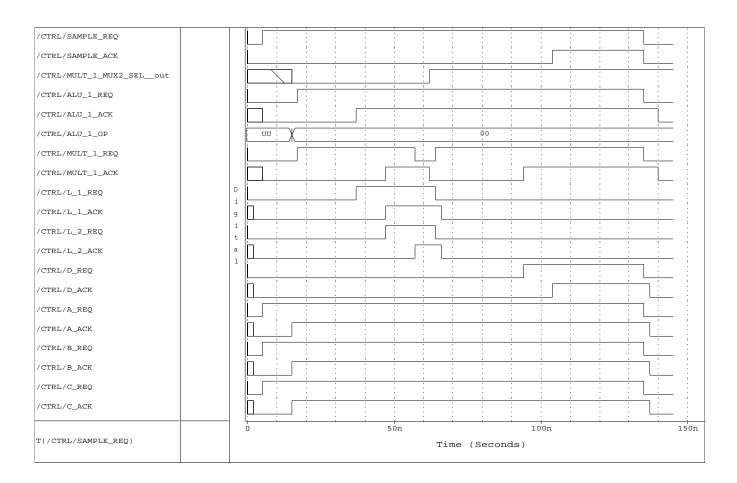

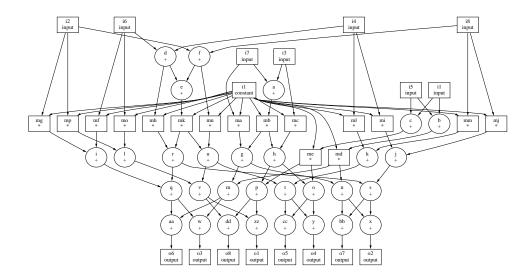

| 2.12 | Structural control generated by the ATACS CAD tool                      | 24 |

| 3.1  | As-soon-as-possible and as-late-as-possible scheduling                  | 28 |

| 3.2  | Critical windows derived from as-soon-as-possible scheduling            | 29 |

| 3.3  | As-soon-as-possible and as-late-as-possible algorithms                  | 30 |

| 3.4  | Force-directed scheduling.                                              | 31 |

| 3.5  | A data flow graph with four operations: A, B, C and D                   | 31 |

| 3.6  | Data flow graphs without and with resource edges.                       | 35 |

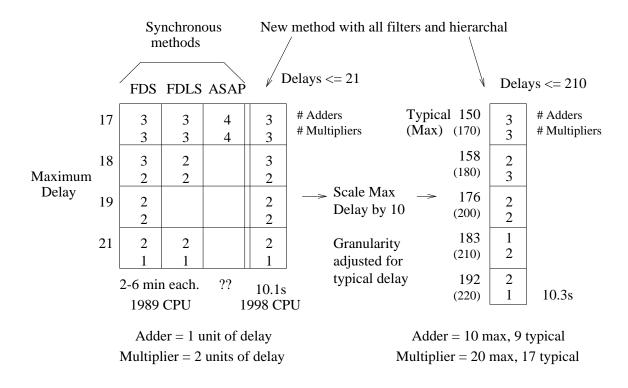

| 3.7  | Synchronous methods vs. asynchronous approach                           | 36 |

| 3.8  | Asynchronous left-edge algorithm                                        | 37 |

| 3.9  | Example using the asynchronous left-edge algorithm.                     | 38 |

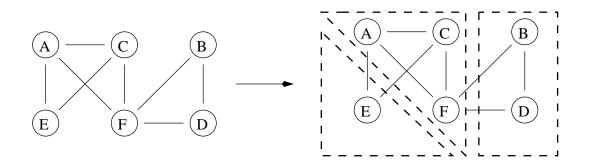

| 3.10 | Compatibility graph for clique covering                                 | 39 |

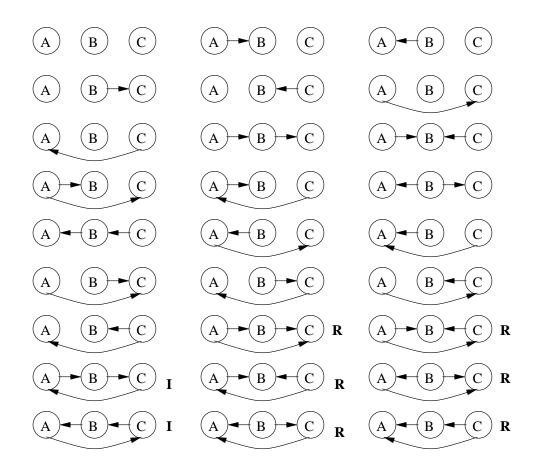

| 4.1  | Exploration space of 3 compatible operations.                           | 42 |

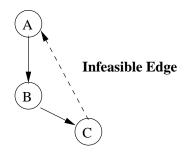

| 4.2  | Infeasible edge                                                         | 44 |

| 4.3  | Procedure to determine if adding a resource edge creates a valid design | 45 |

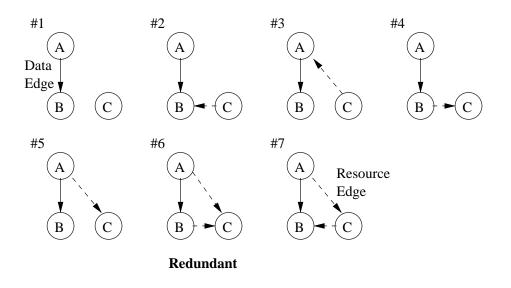

| 4.4  | Design space showing redundancy.                                        | 45 |

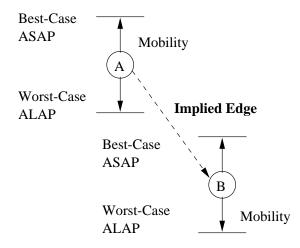

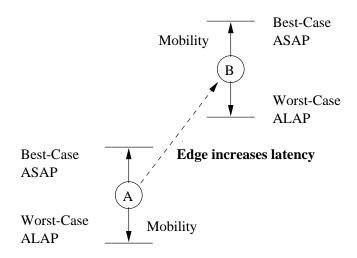

| 4.5  | Implied edge.                                                           | 46 |

| 4.6 | Minimal latency filter.                                      | 48 |

|-----|--------------------------------------------------------------|----|

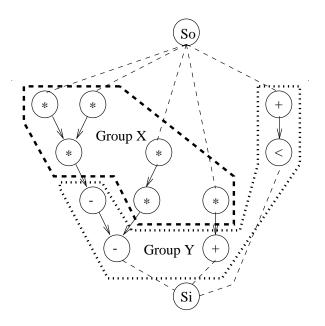

| 4.7 | Grouping of resources for hiearchal exploration              | 50 |

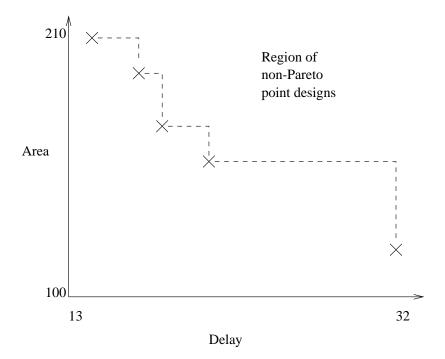

| 5.1 | Pareto Points.                                               | 53 |

| 5.2 | Exploring the design space using a branch-and-bound search   | 54 |

| 5.3 | Exploration tree.                                            | 55 |

| 5.4 | Updating dynamic transitive closure for insertion of an edge | 58 |

| 5.5 | Updating dynamic transitive closure for deletion of an edge  | 58 |

| 5.6 | Updating ASAP schedule for insertion or deletion of an edge  | 59 |

| 5.7 | Updating ALAP schedule for insertion or deletion of an edge  | 59 |

| 6.1 | DIFFEQ: minimum latency solution                             | 64 |

| 6.2 | DIFFEQ: minimum area solution                                | 64 |

| 6.3 | Functional notation for the elliptical wave filter           | 65 |

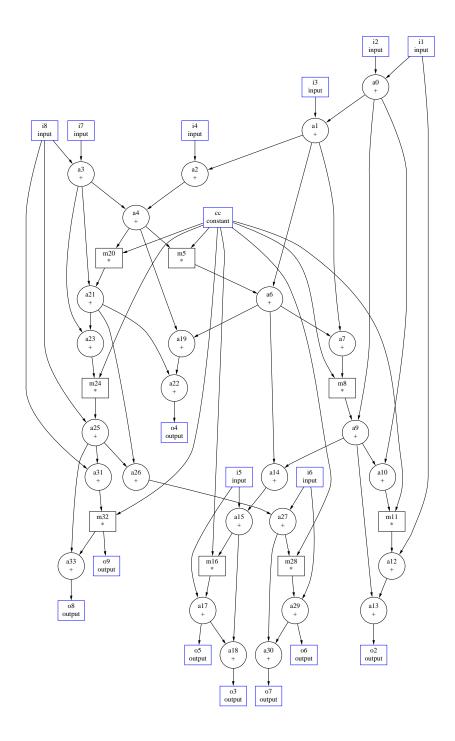

| 6.4 | Elliptical wave filter data flow graph                       | 66 |

| 6.5 | Elliptical wave filter datapath                              | 68 |

| 6.6 | Comparison with synchronous methods.                         | 70 |

| 6.7 | Inverse discrete cosine transform data flow graph            | 72 |

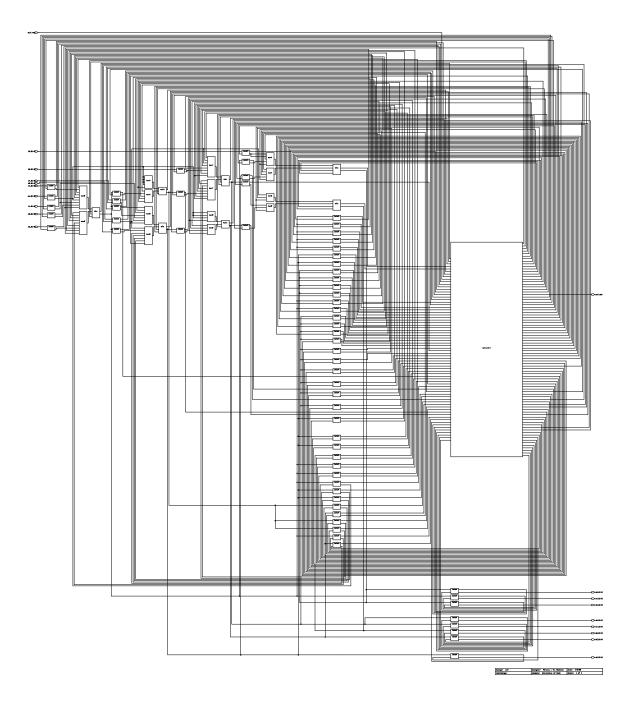

| 6.8 | IDCT: sample minimum latency datapath.                       | 74 |

## LIST OF TABLES

| 6.1 | DIFFEQ: experimental results using nonhierarchal approach      | 62 |

|-----|----------------------------------------------------------------|----|

| 6.2 | DIFFEQ: experimental results using hierarchal approach.        | 63 |

| 6.3 | DIFFEQ: comparison of unique Pareto point solutions.           | 65 |

| 6.4 | EWF: experimental results using hierarchal approach.           | 67 |

| 6.5 | EWF: comparison of unique solutions using hierarchal approach. | 69 |

| 6.6 | IDCT: experimental results using hierarchal approach.          | 73 |

|     |                                                                |    |

## ACKNOWLEDGEMENTS

I am in debt to many people who have made this work possible. Among my colleagues, I am thankful to Robert Thacker for always offering a helping hand, to Wendy Belluomini for much good criticism and advice, to Chris Krieger for many excellent nuggets of understanding, and to Hao Zheng for carrying this work forward. In addition, I would like to thank Luli Josephson for reviewing this work, and Hans Jacobson for his comments.

I would like to express a deep gratitude to my advisor Dr. Chris J. Myers. Over the past several years I have been continually impressed with his constant guidance, technical expertise, and endless encouragement. I would also like to thank Dr. Erik Brunvand and Dr. Christian Schlegel for serving on my supervisory committee. Their comments and assistance have been valuable.

Most of all, I express my thanks to Eric Mercer. I am grateful for his loyal friendship, which included much patience, perseverance, and assistance on my behalf. His savvy technical skills have made this work much better than it would have been otherwise. Through many years of school he has complemented my many weaknesses with strength and he is the unsung hero of this work.

Finally, my wife and family deserve special thanks. I would like to express my gratitude for their love, support, and sacrifice.

## CHAPTER 1

## INTRODUCTION

Sometimes when I consider the tremendous consequences from little things ... a chance word ... a tap on the shoulder or a wink of an eye, I am tempted to think there are no little things.

-Emily Dickensen

Asynchronous designs are rapidly becoming an attractive alternative to synchronous designs. As technology advances, the integrated circuit industry continues to increase clock speeds, increase density, and decrease transistor sizes making global synchronization across large chips more difficult to maintain. To solve this problem, many modern chips have a number of communicating clocking domains which can greatly increase design complexity. As a result, asynchronous design is being looked at as an alternative because it has the potential to reduce, and in some cases, eliminate the growing challenges of synchronous design. Asynchronous circuits consist of groups of independent modules which communicate using handshaking protocols. This makes asynchronous designs attractive because they do not have clock skew problems, thus reducing power-expensive global clocks and routing issues. In addition, asynchronous design offers the potential for average-case performance in place of worst-case performance, they are adaptable to environmental conditions, and exhibit ease in composability. For these reasons, there is a growing interest in asynchronous design.

Architectural-level synthesis is the process of taking an abstract behavioral model of a desired circuit and refining it to an optimal macroscopic structure. In an ideal world, everything would be possible at no cost. But, there are no blank checks in circuit design. Issues such as latency, area, and power must be taken into consideration to balance trade-offs in a design. Architectural-level synthesis is an approach to managing these trade-offs at a macroscopic level.

The abstract model used at the architectural-level generally begins as a *data flow* graph that does not contain implementation parameters such as a mapping to specific

resources or technology. The synthesis process takes this abstract model and generates a structural view of the circuit by determining the necessary resources and parameters to implement the behavioral model. The goal of architectural synthesis is to generate an optimal circuit from an abstract model. The model consists of two components: *datapath* and *control*.

The datapath is the portion of the circuit composed of interconnected components that move data and operate on it. The components are usually multi-bit bused structures that contain a high density of arithmetic functions. The control circuitry directs the movement of data and execution of the datapath resources. When combined, the datapath and control work together to make a circuit functional.

The focus of this research is on the automation of architectural-level synthesis for asynchronous systems. This includes the automated generation of an optimal asynchronous datapath and corresponding control. This work merges methods from synchronous architectural-level design with those used to generate asynchronous control circuits and exploits asynchronous circuit properties to design highly optimized asynchronous systems.

#### 1.1 Motivation

Digital signal-processing, high-speed multimedia, graphics, and telecommunications applications are computationally-intensive. In these applications, the datapath requires the largest area of the logic circuitry, sometimes as much as 80% of a complete design. For these applications the datapath is the critical factor when trying to achieve design objectives such as minimal area and latency. The challenge for a datapath designer is to arrive at the best implementation for a given function. Many datapaths today are hand-crafted using a *Register-Transfer Level* (RTL) specification. Using this model storage of data is represented using register variables, and transformations are represented by arithmetic and logical operators.

Typically, designers arrive at a particular design through trial and error methods. This approach is time-consuming and does not yield optimal results. Furthermore, such designs are rarely scalable to new technologies and it is easy for a designer to lose performance when they commit to a specific design early in a design cycle. To make matters worse, when designers find their datapath to be suboptimal they can rarely afford to go back and redesign it. The continuing trend in the design of *application-specific integrated circuit*

(ASIC) is one of increasing complexity and density, making a trial and error approach increasingly difficult. This leads to the growing need for automated methods which can quickly yield good designs.

The ideal asynchronous design tool would allow designers to quickly generate the desired structure and provide information that would help them determine the best solutions. Each possible solution would be superior in at least one objective, such as size or latency, or in a combination of two or more objectives. This would give the designer the ability to test a variety of good solutions, helping to quickly and efficiently decide on a datapath structure that best implements a function. Automating the design and implementation of such a major portion of the chip would yield substantial reductions in design time, increase productivity, ease specification, modification, and enhance design re-usability.

#### 1.2 Related Work

It is a common practice for synchronous circuits to be formally modeled and automatically synthesized. There are many existing tools which support automatic translation of an algorithmic-level specification to a register-transfer level representation [22]. The use of such models and automated tools for asynchronous circuits has been limited to synthesizing control circuitry. Thus, many systems exist for the synthesis of untimed asynchronous control circuits [27].

A number of different styles for designing asynchronous control circuits exist. One method is to constrain signals to change only one at a time. The system must allow each signal time to settle before other signals can change [41]. This is called the *fundamental-mode* restriction. *Burst-mode* extends fundamental-mode to allow for a set, or burst, of inputs to arrive concurrently, followed by a burst of outputs [17, 35, 45]. Another method, *delay-insensitive* [12, 19, 33] assumes that the delays in wires and gates are unbounded. *Speed-independent* circuits [6, 16, 32] are similar, but assume that wire delays are negligible. Most methods are based on the assumption that nothing is known about the delays between signal transitions. This means that the circuit must be constrained to work correctly even in cases which never occur in physical implementations.

For asynchronous control circuits, an emerging area of research embraces timed asynchronous circuits [34]. This method allows a lower and an upper timing bound to be assigned to the relationships between signals. These circuits make use of the timing information to eliminate unnecessary circuitry and to increase performance.

At the architectural-level, tools that automate datapath synthesis are just emerging. Heuristic techniques for synchronous design have been extended to asynchronous circuits [5], but many require the designer to manually specify where resources are shared [2, 8]. Work has also been done by Beerel to extend the synchronous techniques in [25] by using a mixed-integer linear programming technique to yield globally optimal solutions.

This work is related to work previously done in synchronous architectural-level synthesis and also work done in the area of asynchronous control circuits. For synchronous architectural-level synthesis, a vast array of algorithms and tools have been proposed. In general, these optimization problems are intractable and their solutions depend on solving associated sub-problems.

The subproblems are usually also intractable and are often solved through the use of heuristics. The subproblems are categorized into general areas which include *binding*, *allocation*, and *scheduling*. Binding is the process of mapping an operation to a resource. Where several resources can perform the same operation, the problem is extended to a *module selection* problem. When more than one operation has the same type, *resource sharing* or allocation can be employed. Allocation determines the quantity of each type of resource used to implement the operations. Scheduling is the process of denoting each operation's start time subject to precedence constraints specified by a data flow graph.

To solve the scheduling problem, it is broken down in its simplest form to a unitdelay model in which all operations have equivalent delay. Different algorithms have been proposed to address constrained and unconstrained scheduling of individual operations. These algorithms include unconstrained *as-soon-as-possible* (ASAP) scheduling, and latency-constrained *as-late-as-possible* (ALAP) scheduling [18]. These algorithms are specific to synchronous design problems. This research modifies these algorithms for application to asynchronous optimization problems.

Scheduling with resource constraints is also very important because with resource dominated circuits, resource usage determines the circuit area. Solutions have been developed using an exact integer linear-programming model [24, 13]. This approach is suitable for medium scale examples, but fails to solve problems with a large number of variables or constraints. Another method is *force directed scheduling* (FDS) [36]. This method attempts to use the concept of force to optimally schedule operations. All these algorithms are currently restricted to synchronous design problems.

The timed models used for control circuits motivate the use of delay assumptions in datapath resources. When a timed model is applied to asynchronous datapath resources, the design evaluation space can be reduced, unnecessary circuitry eliminated, and increased performance achieved. The work described here is designed to be used in conjunction with the ATACS tool framework [34], which can further refine the generated asynchronous control circuitry. The result is a completely automated tool flow for refining asynchronous specifications from a behavioral level to a structural level.

### **1.3 Contributions**

The focus of this work has been to explore and develop a method of architectural-level synthesis for asynchronous circuits. In particular, the issues of scheduling and allocation for asynchronous resources are confronted. While binding and resource selection are also important issues that can affect scheduling and allocation this study does not attempt to utilize their potential benefits at this time.

For asynchronous circuits to become a viable and superior alternative to synchronous circuits, good asynchronous computer-aided design tools need to be created. These tools, at a minimum, need to have comparable functionality to synchronous tools while maintaining a similar ease of use. Since developing such tools would be a very large and time consuming process, it is argued that asynchronous tools should build on work already done and that they should be as compatible as reasonably possible with current synchronous tools. This would expedite the transition for designers from synchronous design to asynchronous design without learning a completely re-engineered design process.

Scheduling optimization problems use synchronous techniques to find critical windows of time for resources with asynchronous delays. Relative timing of operations is used in conjunction with the analysis of the critical window of operations. From this, an estimate of the typical delay of each configuration may be made. Furthermore, for allocating resources to specific operations, a technique was developed that uses information from scheduling in conjunction with the information derived from the data flow graph. Using both sources of information, a heuristic algorithm efficiently solves the allocation problem.

Exploring all possible configurations to implement a given design is difficult because the number of possible solutions grows exponentially with respect to the size of the data flow graph. Several exact and heuristic filters to reduce the size of the design space are implemented. These filters are very effective in reducing the exploration time for the circuit design. These filters include: pruning the design space when implied edges are detected, removing redundant designs from consideration, solving for a minimal-latency solution efficiently, and detecting when a maximal configuration is achieved without exploring an entire branch of the design space. Several case studies illustrate the effectiveness of these filters.

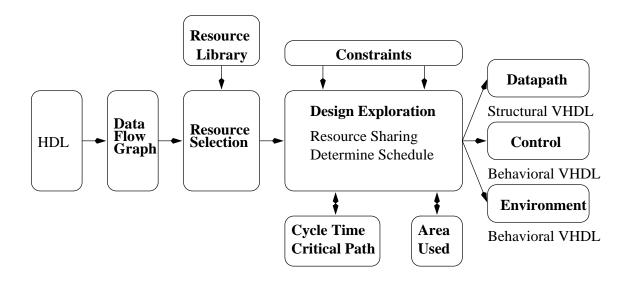

This study necessitated a CAD tool for experimenting with the various automatic methods of scheduling, allocation, design space exploration, and the effect of the proposed filters. The CAD tool Mercury has been developed for this purpose. Figure 1.1 shows the design flow of the tool. Mercury is unique in that it can take an abstract model of a design, in this case a data flow graph, and from that generate both an optimal structural view of an asynchronous datapath for the design, as well as the necessary behavioral control to coordinate that datapath. The generated structural view consists of an interconnected block diagram of functional units, latches, control, and multiplexors.

The generated asynchronous control can be refined further to logic gates using the existing ATACS tool. The end result is a fully specified asynchronous design which can be tested and verified. Mercury implements these ideas by generating output which can leverage synchronous tools for a common framework of simulation and functional verification. Furthermore, the development and use of Mercury demonstrates the idea that a CAD tool can generate a reliable and efficient asynchronous circuit for minimum cost and design time.

#### 1.4 Thesis Outline

Chapter 2 discusses issues relating to the architectural modeling of asynchronous designs. Mercury's model input format and intermediate circuit representations are examined. The chapter continues with a description of then generation of a structural view of the datapath and a behavioral view of the control from an abstract model. The chapter concludes with an illustration of how the resource and constraint libraries are modeled. The exponential nature of the design space is reviewed in Chapter 3. The chapter continues with illustrations of how each configuration in the design space is evaluated using asynchronous versions of binding, scheduling, and resource allocation. These techniques are compared and contrasted with traditional synchronous methods. The study proceeds with a discussion in Chapter 4 of the proposed methods of using filters to reduce the design space. Several filters are presented, some of which are exact

Figure 1.1. Mercury design flow.

and others which are heuristic. Chapter 5 describes the algorithm used to explore the design space. Optimizations used to reduce the execution time of exploration are also illustrated. These optimizations include using dynamic transitive closure and dynamic path analysis. Several case studies for using the presented methods to build asynchronous circuits are presented in Chapter 6. In the case studies, the effectiveness of each filter is given, along with examples of the resulting asynchronous circuits. Chapter 7 summarizes the contributions and results of this work and offers ideas for possible extensions.

### CHAPTER 2

## ARCHITECTURAL LEVEL MODELING

Mistrust endeavors which require new clothes. —E. M. Forster

### 2.1 Representation and Modeling

It is often beneficial to simplify a circuit representation with a model. A useful model contains all of the relevant design features without including implementation details. These models give designers and CAD tools a common method of conveying information about a circuit. Circuits can be modeled differently according to the desired level of abstraction. Stages of abstraction include, but are not limited to, architectural, logic, and transistor. For example, at the architectural level, circuits are modeled showing required operations and their dependencies. At the logic level, circuits are modeled with interconnected logic blocks and logic networks. At the transistor level a physical view of the circuit is modeled.

Generally the design of a circuit progresses through these various tiers of abstraction until a physical view of the circuit is obtained. At each stage, the model of the circuit becomes less abstract as successively finer detail is introduced. Each level adds just enough information to capture essential features of that level. Before progressing to the next step, the model can be simulated, validated, and verified.

The top level of the design process, the most abstract, is the architectural-level. Here, the function of the entire system is described in algorithmic terms with the behavior of a circuit being modeled in a hardware description language (HDL). Consequently, this level of modeling is often referred to as behavioral modeling. An HDL provides well-defined semantics and syntax for a model. This gives a consistent and unambiguous representation of a specification which can be used to exchange information between designers and tools.

Although HDLs such as VHDL and Verilog evolved from traditional programming languages, they are different in many ways. For example, they generally default to concurrent operations in place of statements which execute sequentially. In this regard, HDLs are related more closely to parallel programming languages than to traditional sequential programming languages. HDLs also allow for the definition of ports into and out of the circuit, along with their required data formats and parameters. HDLs place a large emphasis on the specification of detailed timing constraints for each circuit component. In addition, many of the HDLs support different views for a circuit. For example, a behavioral view and a structural view are typically supported. Architectural-level synthesis tools generally support the transformation of behavioral models into structural models.

Using such a formally defined model is beneficial for several reasons. First and foremost, when a system design is needed the system requirements can be specified unambiguously and completely. Engineers have the task of designing a system that meets customer requirements. Using a formal model to specify the system requirements reduces the risk of incomplete or ambiguous specifications. It also gives the engineer the opportunity to explore alternative implementations, and find the best design, given the customer's criteria.

Second, formal modeling allows for design validation and verification. Using a hierarchal approach, subsystems and subcomponents can be individually tested. At each level in the design hierarchy, the composite system can be tested and verified. While functional validation is useful, models can also be used as a starting point to formal design verification. Formal verification uses formal logic and rules of inference to deduce the correctness of a design. Formal verification is a complex problem itself and is an active area of research for both synchronous and asynchronous circuits [3, 7, 38]. While formal verification is not yet an everyday practice, there has already been significant progress in this area and there is an optimistic horizon in its future.

Finally, a formal model allows synthesizing a circuit automatically. If a design can be formally specified, it can, in theory, be translated to a circuit that performs that function. The automated generation of circuits is beneficial because it reduces the time of a design and thus, more time can be spent exploring alternative designs rather than being consumed with the details of a particular design. Furthermore, if the translation is automated and the translation process itself is verified, then confidence that the resulting circuit is correct rises.

In essence, a formal model used in conjunction with computer-aided design tools is

a means to achieving a reliable and efficient circuit for minimal cost and with minimum design time. By providing better tools for the design process, many errors can be avoided, delays minimized, and costs contained.

For this work, VHDL [4, 43] is used. VHDL is a verbose language used to specify and document large systems. It is used to model both the control and the datapath of a design. VHDL is employed to model the control, in part, because it can be simulated and verified using current synchronous CAD tools and also because a subset of the language can be successfully compiled into a format that can be synthesized into a timed asynchronous control circuit [46].

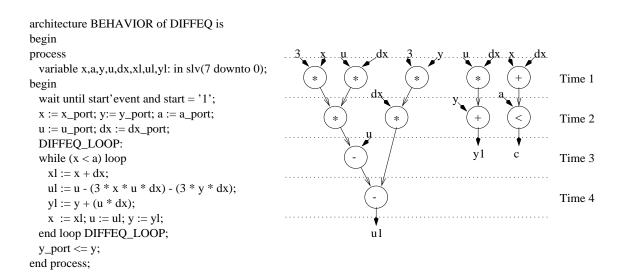

The first step in the design process is to take a formal behavioral model and translate it into a representation that illustrates the flow of data from one operation to the next. Figure 2.1 shows the behavioral VHDL representation of a differential equation solver with its corresponding data flow graph.

The refinement of the VHDL model into a good data flow graph is a difficult task because several optimizations are possible. These optimizations include: tree-height reduction, constant and variable propagation, common subexpression elimination, and dead code elimination. Each of these optimizations affects the resulting data flow graph, which in turn limits or enhances the synthesis process. Methods from compiler theory have been developed in [1, 42] which solve these and similar problems. It is assumed that

Figure 2.1. Behavioral VHDL and corresponding data flow graph.

these optimizations have been made and translation to a data flow graph has already taken place, so Mercury accepts input in the format of a data flow graph similar to that shown in Figure 2.1.

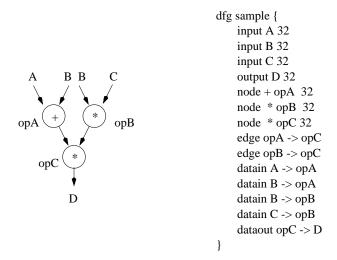

A data flow graph is relatively simple to specify. Textually, the format given in Figure 2.2 is used. It first defines the name of the graph, then lists each of the primary inputs and primary outputs of the system with their corresponding sizes. Next, nodes in the graph are listed with their operation type, name, and size. The nodes are linked together using edges. An edge can exist between any two nodes as long as the edge does not create a cycle in the graph. Finally, inputs are linked to nodes which utilize them, and outputs emanate from nodes that produce them.

It should be noted that the user can optionally specify an ordering for input operands to a node. This can be important when an operation, such as subtraction, is noncommutative. If an ordering is not specified, then the operations are evaluated according to alphabetical order. Using this format allows the function of the circuit to be modeled. Figure 2.3 shows a sample data flow graph and its corresponding specification. This model permits a design to be further refined using binding, scheduling, and allocation.

```

dfg name {

input in-name bit-width

input in-name bit-width

output out-name bit-width

ouput out-name bit-width

node operation node-name bit-width

. . .

node operation node-name bit-width

edge node-name \rightarrow node-name port

. . .

edge node-name \rightarrow node-name port

datain in-name \rightarrow node-name port

datain in-name \rightarrow node-name port

dataout node-name \rightarrow out-name

dataout node-name \rightarrow out-name

}

```

Figure 2.2. Input format for a data flow graph (DFG).

Figure 2.3. Sample data flow graph and model description.

### 2.2 Modeling Resources

To unify the design process, some underlying requirements must be made about functions in the resource library. Here it is required that each resource in the library is an asynchronous system that follows a specific communication protocol. None of the resources are synchronized by a global clock. A protocol is a sequence of events in a communication transaction. Many handshaking protocols exist, such as two-phase transition signaling or four-phase signaling. For these two predominate methods, there is ongoing debate concerning the better choice. The four-phase protocol requires twice as many actions as two-phase, but the actions are usually simpler. In general, when operator delays dominate communication costs, then four-phase is better. Four-phase may also be better for precharged arithmetic units since the return to zero naturally fits the precharge phase. When transmission delays dominate communication costs, two-phase is better.

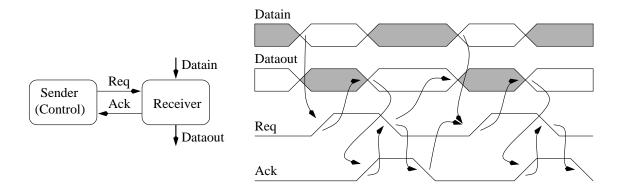

Mercury currently supports only the four-phase protocol with a bundled data path. The bundled-data approach uses a set of control wires to indicate the validity of a set, or *bundle* of data wires. Similar self-timed modules that follow a two-phase protocol are used in [11]. In either protocol, the control wires for each bundle include two signals. The first signal is used to request (REQ) an action. Once the receiver of the request has completed its function it sends an acknowledgement (ACK) back to the sender to complete the transaction. Figure 2.4 illustrates the request/acknowledge protocol. With

Figure 2.4. Request/acknowledge interface with four-phase handshake protocol.

a four-phase protocol, each signal transition is considered along with its direction of movement. For example, a rising request is distinguished from a falling request. There are several methods of employing the four-phase handshake, including, *early*, *late*, and *broad* protocols [20].

Mercury uses the *early* protocol in which the rising edge of the request line indicates that data is available, and the rising edge of the acknowledge line indicates that the computation has been completed and the sender no longer needs to hold the inputs stable. The falling edge of the ACK signal resets the component to an *available* state. The bundled data approach requires data in the bundle to be valid at the receiver before the receiver sees a change on the control signals. In figure 2.4 the light regions indicate when data are valid and the shaded regions indicate when data are invalid.

For simplicity, it is assumed that the interface of each device is delay-insensitive. This means that the protocol is insensitive to delays through circuit components and the wires that connect them. Obviously, this does not accurately model the physical properties of system components and wires. This makes building a truly delay-insensitive circuit difficult, as demonstrated by [30]. This issue is left for the next level of refinement in the synthesis process.

Although self-timed delay-insensitive circuits involve signaling overhead for the handshake communication, they offer several appealing advantages. Generally, they give better performance than synchronous systems because they tend to reflect average-case delays rather than worst-case delays for a system. In some cases, this alone can be a major performance benefit. Second, they allow a system to be upgraded incrementally. Each component can be individually replaced without changing or doing extensive redesign of the entire system. Third, very robust systems can be implemented because timing and functionality are separated. For example, when a circuit is required to operate over a wide range of voltage and temperature conditions, self-timed systems are ideal because they easily adapt to their environment. Finally, self-timed components allow the construction of systems in a hierarchical and uniform fashion. This characteristic is very beneficial because designs can be assembled without considering detailed timing characteristics. When timing characteristics are available and considered, the circuit can be more aggressively optimized.

Using the self-timed circuit methodology, asynchronous resources are annotated in the resource library with timing information. This information is used to optimize the configuration of resources. Each supported function of a given resource is modeled with a minimum, maximum, and typical computational delay. These correspond to the datadependent computational delays of each function. For this work, it is required that operations have bounded delays. In addition, the area and the bit-width of each resource must be given. The order in which the functional units are listed for a resource determines the operation select code used by control to select the proper operation. Figure 2.5 shows the input format of the resource library. The user can use standard operations such as addition, subtraction, and multiplication, or can create more complex custom resources and operations.

For the best results, the parameters of each resource should correspond to the physical properties of the resource. Each library generally maps to a specific technology. This

```

drl name {

resource-name bit-width area

operation-type [min-delay,max-delay,typ-delay]

...

operation-name [min-delay,max-delay,typ-delay]

...

resource-name bit-width area

operation-type [min-delay,max-delay,typ-delay]

...

operation-name [min-delay,max-delay,typ-delay]

...

operation-name [min-delay,max-delay,typ-delay]

...

}

}

```

gives a modular approach that leaves room for expansion to future technologies without requiring a change in the specifications of a design. A small sample library is shown in Figure 2.6.

## 2.3 System Constraints

Constraints on the design can also be specified. These are valuable because they can focus the design search, reducing the time required to achieve a good solution. The user can specify an upper limit on both the desired area and the desired delay. For example, if the user sets a maximum desired delay for a system, the tool stops exploration (evaluating all possible configurations) of any branch where that value of latency is exceeded, yielding a significant savings in execution time.

The user can also specify the maximum number of instances for any particular resource type. The format for specifying these values is shown in Figure 2.7. The use of constraints is optional, but they are usually beneficial for large designs, because the more constrained a design is, the quicker a good solution can be found. A sample constraints specification is shown in Figure 2.8.

```

drl myLib {

ALU 32 452

+ [12,28,15]

- [12,30,16]

Multiplier 32 671

* [34,82,61]

}

```

Figure 2.6. Sample datapath resource library (DRL).

```

constraints name {

max-area = val

max-delay = val

resource-name = val

...

resource-name = val

}

```

```

constraints myCon {

max-area = 923

max-delay = 102

ALU = 1

Multiplier = 1

}

```

#### Figure 2.8. Sample constraints specification.

#### 2.4 Output

At this level, the goal of refinement is to generate an optimized structural view of a system from a behavioral description. Using the three sources of information—a data flow graph, a library of functional resources, and a set of constraints—all the necessary information to refine the system is available. In Mercury, after a data flow graph has been bound, scheduled, and allocated, a structural view of the datapath is generated and a behavioral view of control for the datapath is also generated. Both views are specified by Mercury using VHDL. The following sections describe these processes.

#### 2.4.1 Datapath Generation

The datapath is organized as follows. First, latches are instantiated for each of the primary inputs, outputs, and data edges in the data flow graph. Latches for the outputs are not always required. They are only required when a functional unit is resued for other operations after the output is generated. In other words, in cases where the functional unit can not hold the output for the duration of the system. This relaxes the requirement for latches on all outputs. This optimization however, is not currently implemented. Next, Each functional unit is instantiated and when more than one operation is mapped to the same functional unit, multiplexors are used to route the appropriate operands at the appropriate time. At the output of the functional unit, latches are used to carry the data to the next operation, or to the primary outputs. This datapath format is illustrated in Figure 2.9.

Figure 2.10 shows one possible arrangement for the datapath generated by the Mercury tool from the specification given in Figure 2.3. The datapath works in the following way. When the global request signal, *sample\_req*, is asserted, data from the primary inputs are latched. When all of the required operands for a given computation are available, and the functional unit is available, the computation begins. In the example given in Figure 2.10,

Figure 2.9. Datapath format.

Figure 2.10. Datapath generated from sample model description.

the multiplier is shared between two operations, requiring two 2x1 multiplexors to be used (one for each operand).

After each computation is completed, the results are stored in a latch for future use by other operations and the functional unit then becomes available for its next operation. Finally, the system acknowledges on the *sample\_ack* signal it has completed its computation when all of the primary outputs have latched their data.

While the entire system is modeled in this way, each subcomponent of the system is also modeled with a similar protocol. In the example, the ALU and multiplier, when requested, also latch their inputs, and hold their outputs until their results are acknowledged by their environment. This allows components to be generated and used in a hierarchal fashion. The only exception to this protocol is a multiplexor component, because it does not latch its inputs or its outputs.

Additional optimizations can be made to the datapath to reduce the number of latches required to implement a system. Sharing latches that hold data for disjoint periods of time is one such optimization. This, however, is a difficult problem to solve because of the inherently asynchronous lifetime of data. In theory, this problem is similar to the resource sharing problem, in that the sharing of latches can incur the use of additional multiplexors, which in turn require more area, and the additional complexity usually complicates the control further. For these reasons, and in order to simplify the generation of the datapath and control, this optimization is not currently applied.

To generate the datapath, Mercury takes a bound, scheduled, and allocated data flow graph and builds a VHDL model. A sample VHDL structural model for the datapath is listed in Appendix A. This model corresponds to the behavioral model shown in Figure 2.10. The generation of the model begins by first defining the entity of the primary system with primary outputs, inputs, and handshaking signals. For the structural architecture of the entity, the components used by the system are declared. In the example, the components ALU, Mult, mux2, latch, and CTRL, are all declared. The components refer to resources defined in the library shown in Figure 2.6, except for the controller component, CTRL and multiplexors, which Mercury generates.

Next, intermediate signals are declared. These are the signals which are used between the ports of the latches, multipliers, controller, and functional units. All of these signals are internal to the system. After the signals are declared, each of the required components is then instantiated. Where more than one instance of a device is used allowing concurrent operation, multiple instantiations are declared. Where operations are serialized and more than one operation is mapped to an individual resource, multiplexors are instantiated to select the data. Finally, the ports of each of the components are wired up to the appropriate signals to complete the design of the datapath.

#### 2.4.2 Control Generation

Generating the control corresponding to a particular configuration of the datapath is determined, in part, by the protocol used between components. Each of the components in the datapath follows a four-phase handshake protocol using request and acknowledge signals. Following this protocol, Mercury builds a control module for each datapath configuration.

The control is built using the request and acknowledge signals from each of the components, such as functional units, latches, and the primary request and acknowledge signals. When multiplexors are used, their select bits are generated by the control but no handshaking signals. Using VHDL, the communication protocol of each component is modeled with VHDL processes. When a process is activated during simulation, it starts executing from the first statement and continues until it reaches the last. All statements in a process take zero simulation time except for "wait" statements. So, it is only through the execution of "wait" statements that simulation time advances. Each process executes concurrently with respect to other processes. The behavioral VHDL for the controller is shown in Appendix B.

Each instance of a latch in the system is modeled in the control with an individual process. Each latch is initially unoccupied. Latches on primary inputs wait on the primary request of the system. The data are latched when the primary request is received. These latches return to an available state when the entire system has been acknowledged. Shown below is an example of this type of process:

```

-- controls latch l_A at the source

proc5:process

begin

wait until sample_req = '1';

A_req <= '1' after delay(2,4);

wait until sample_req = '0';

A_req <= '0' after delay(2,4);

end process;</pre>

```

Each functional unit instance is modeled with a unique process. Because each func-

tional unit can be used for more than one operation, these processes control the ordering of each operation using the resource. This is done by waiting for the appropriate operands to become available. When they become available, the multiplexors are set, and the correct data is steered to the functional unit. The functional units reset to an available state after they have completed their operations. Shown below is an example of this type of process:

```

-- controls resource Mult_1

proc9:process

begin

wait until Mult_1_ack = '0' and B_ack = '1' and

C_ack = '1' and sample_req = '1';

Mult_1_mux2_sel <= '0' after delay(0,1);</pre>

Mult_1_req <= '1' after delay(2,4);</pre>

wait until l_2_ack = '1';

Mult_1_req <= '0' after delay(2,4);</pre>

wait until Mult_1_ack = '0' and l_1_ack = '1' and

l_2_ack = '1' and sample_req = '1';

Mult_1_mux2_sel <= '1' after delay(0,1);</pre>

Mult_1_req <= '1' after delay(2,4);</pre>

wait until D_ack = '1';

Mult_1_req <= '0' after delay(2,4);</pre>

wait until sample_req = '0';

end process;

```

Intermediate latches between operations wait for acknowledgement from the preceding computation before latching the resulting data. The latch then waits for the resource that uses that data to be requested before returning to an available state. Where many operations are performed by a single resource, the select bits of the multiplexor are used to ensure the resource is performing the right computation on the correct data values. Sequencing of operations is handled by the control. Shown below is an example of this type of process:

```

-- controls latch between nodes opA and opC

proc1:process

begin

wait until ALU_1_ack = '1';

l_1_req <= '1' after delay(2,4);

wait until Mult_1_req = '1' and Mult_1_mux2_sel = '1';

l_1_req <= '0' after delay(2,4);

end process;</pre>

```

When all the primary outputs of the system have acknowledged, the system's primary

acknowledge is asserted. After the environment responds by lowering the request signal, the entire system is reset to an available state. Shown below is an example of this process.

```

-- controls the ack of the entire system

proc3:process

begin

wait until D_ack = '1' and sample_req = '1';

sample_ack <= '1' after delay(2,4);

wait until D_ack = '0' and sample_req = '0';

sample_ack <= '0' after delay(2,4);

end process;</pre>

```

Using this control specification, Mercury is compatible with synchronous VHDL simulators. Figure 2.11 shows a wave diagram for the handshaking signals of the control. The simulation was done using ViewLogic's VHDL simulator FusionSpeedwave.

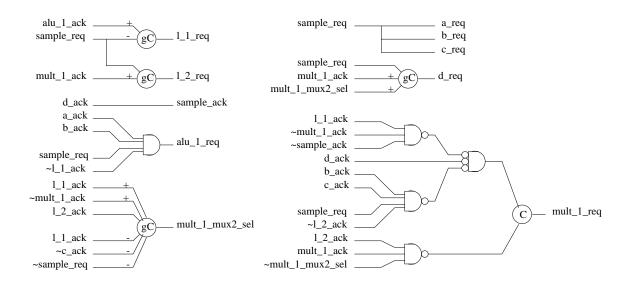

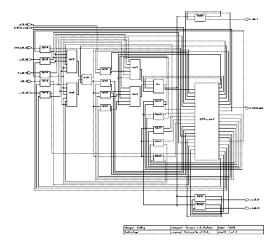

In addition, this model of the control is compatible with the asynchronous CAD tool ATACS [46, 34], which is designed to further refine the control to a gate-level model. Figure 2.12 shows a view of the control generated by ATACS using the behavioral VHDL description. The control has 40 literals and requires 94 transistors to implement.

For ease in compilation, simulation, and verification, a VHDL configuration is often very useful. The configuration maps each instance of a component to a specific VHDL architecture model of that component. Appendix C shows a sample configuration generated by Mercury.

| Figure 2.11.          |

|-----------------------|

| Timing                |

| diagram :             |

| showing               |

| handshaking protocol. |

$\frac{23}{3}$

Figure 2.12. Structural control generated by the ATACS CAD tool.

# CHAPTER 3

# DESIGN SPACE EXPLORATION

The real voyage of discovery consists not in seeking new landscapes, but in having new eyes. —Marcel Proust

Many different valid hardware implementations may exist for a given data flow graph, each with a specific configuration of hardware resources and corresponding control logic. The set of possible configurations is the *design space* of the system. For efficiency and structure, the exploration of the design space is divided into three main subtasks: binding, scheduling, and allocation. As discussed in Chapter 2, binding determines a mapping between operations in the data flow graph and resources in a library. Scheduling determines when operations are executed, and allocation determines which resources can be shared between operations, giving the quantity of each type of resource used to implement the operations in the data flow graph.

Some systems perform binding and allocation followed by scheduling [14, 31]. In these methods, delay and area information is estimated and then back-annotated for verification. Other methods perform scheduling before binding and allocation [21, 40]. This approach works well for resource-dominated circuits such as DSP and processor designs. ASIC circuits, however, are generally not resource dominated but control dominated, and therefore perform binding before scheduling and allocation. This permits estimating the required steering logic and also allows for a more precise assessment of delays. In this case, the scheduling problem is not constrained by binding or allocation and it can be solved efficiently. Binding and allocation, however, generally dominate the complexity of the problem [18, 15].

In an asynchronous circuit, an operation can execute as soon as the resource to which it is bound is available and all of its data inputs are available. Since time steps are not explicit and timing is not discrete, it is unclear how to effectively apply the tasks of binding, scheduling, and allocation. Mercury uses a hybrid approach in which it directly extends the principles of synchronous scheduling. First, binding is performed, then scheduling and allocation are performed to determine the timing and allocation of resources. When accurate models are used for area, delay, and interconnect, this approach can work for both resource-dominated and non-resource-dominated circuits.

# 3.1 Binding

The first step is to create a binding for the operations in a data flow graph. This determines a mapping between operations in a data flow graph and resources. A binding may associate more than one operation to a specific resource type in the library. A covering relationship can be defined among types to represent the fact that a resource implements more than one operation. For example, an ALU may cover several operations like addition and subtraction.

In order to produce a valid binding it is necessary that all operations are bound to a library resource. Where this is not the case, a *partial binding* is created. Mercury does not consider nor allow partial bindings because this would prevent a data flow graph from being accurately scheduled and allocated.

There is currently a limited supply of asynchronous components in which to build a circuit. Therefore, Mercury does not focus on binding and resource selection. While binding and resource selection are important issues, their potential benefits are not utilized at this time. For simplicity, Mercury requires that the library contains at least one resource to satisfy each operation type used in the data flow graph. Then, to perform binding, Mercury binds the first resource in the library which satisfies the operation.

# 3.2 Scheduling

For synchronous systems, scheduling determines when operations are executed in time. This can be done efficiently using discrete-time intervals based on a global clock. In an asynchronous circuit, the absence of a global clock and the asynchronous timing of events make scheduling difficult. The scheduling of resources is dependent only on the availability of the resource and its inputs. For accurate asynchronous scheduling, resources must be modeled with data-dependent completion delays. Since binding is done prior to scheduling, delay information is extracted from the given binding.

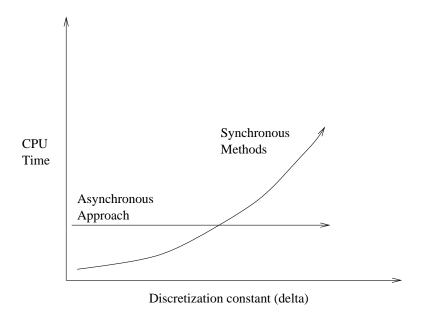

Traditional scheduling of synchronous designs assigns a given start and finish time with each operation. In asynchronous scheduling, the start and finish times of operations have a limited use because data-dependent delays have a significant impact on performance [9]. While scheduling information is useful, it has a limited use in asynchronous design because it is very difficult to break time into discrete bins. Furthermore, discrete methods rapidly become computationally infeasible as discretization constants are made small to allow for finer granularity.

For these reasons, scheduling information is not used here to explicitly schedule an operation to a specific time. It is only used to determine conservative windows of time in which a operation *may* occur. The actual schedule is determined by resource sharing and the order of operations. This makes the scheduling of operations for asynchronous design an optional task. It is shown later, however, that this scheduling information can be very helpful in reducing the time required to find a good solution. We leverage synchronous methods to find the potential start and finish times of each operation.

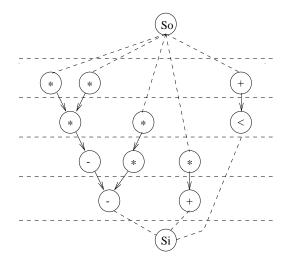

For these tasks, two common algorithms are used. Mercury uses the synchronous method of ASAP (as-soon-as-possible) scheduling to find the conservative windows of time in which an operation may be utilizing a resource. ALAP (as-late-as-possible) scheduling is used in conjunction with ASAP scheduling to find the *mobility* of each operation in the data flow graph [18]. The following sections describe these methods.

### 3.2.1 ASAP Scheduling

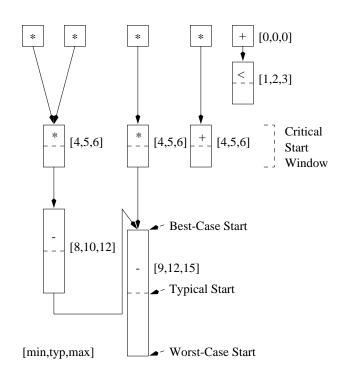

ASAP scheduling, or scheduling without resource constraints, is used to determine a lower bound on the latency of the system. ASAP scheduling is solved in polynomial time by iterating through the nodes of the data flow graph in topological order. Each node is scheduled by setting its start time to the maximum ending time of all its predecessors. The ending time of each operation is computed by adding either the minimum, maximum, or typical delay of the operation to its starting time. This gives three ASAP schedules for each operation.

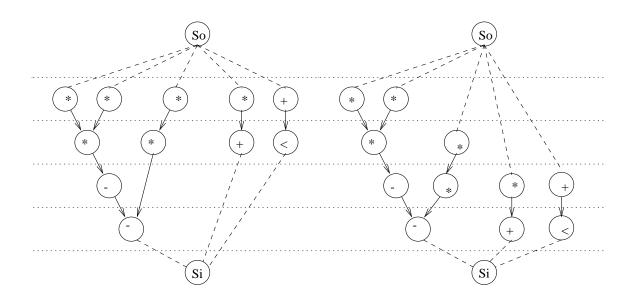

Figure 3.1a illustrates how the synchronous ASAP algorithm would schedule resources for the differential equation solver. The ASAP algorithm is shown in Figure 3.3. Because resources can be scheduled without limit, configurations that limit the number of resources only have a latency greater than or equal to that of the unconstrained ASAP schedule.

By design, operations in an asynchronous system always start as soon as they can. This means the difference between a minimum (best-case) ASAP schedule and maximum (worst-case) ASAP schedule yields a range of time in which the operation starts its computation. In this manner, scheduling takes on a nontraditional definition. Namely, scheduling involves denoting an operation with a window of time when a resource is most likely used for a given operation. These ranges of time are called *critical windows* because these windows are used during resource sharing to determine the range of time when other operations should not try to utilize a given resource to avoid resource conflicts. Resource conflicts lead to a loss in performance because one operation may have to wait for the resource to become available.

Using the data flow graph from Figure 3.1, each node is scheduled as-soon-as-possible using a minimum, maximum and typical delay. For this example, it is assumed that each multiplication operation has a minimum delay of four, a typical delay of five, and a maximum delay of six. All other operations have a minimum delay of one, typical delay of two, and maximum delay of three. Figure 3.2 shows the critical windows for the start times of each operation determined by ASAP scheduling for the differential equation solver example.

## 3.2.2 ALAP Scheduling

ALAP scheduling is the complement of ASAP scheduling and is used for latencyconstrained scheduling. In this case, operations are scheduled as late as possible by setting the finish time for each operation to be the minimum start time of all of its successors. Again, like the ASAP algorithm, unless explicitly constrained, resources can

Figure 3.1. As-soon-as-possible and as-late-as-possible scheduling.

Figure 3.2. Critical windows derived from as-soon-as-possible scheduling.

be used without limit.

The ALAP algorithm is shown in Figure 3.3. The variable  $\kappa$  is the latency bound, and is chosen to be the delay of the schedule computed by the ASAP algorithm. Again, best-case, worst-case, and typical ALAP schedules are derived using minimum, maximum, and typical data-dependent resource delays respectively. Figure 3.1 illustrates how the synchronous ALAP algorithm would schedule resources for the differential equation solver. The computational complexity of both ASAP and ALAP is O(V+E).

## 3.2.3 Mobility

Using the difference of ALAP and ASAP scheduling, the mobility of each operation is computed. This is an important quantity because it represents the span of time in which an operation may be started. To illustrate, assume that for a specific operation the best-case ASAP start time is 5, and the best-case ALAP start time is 18. Then the mobility of the operation is 13.

If an operation has zero mobility then it is started only at a single given time, or else the schedule would exceed the calculated latency. The critical path of the system

```

\begin{array}{l} \text{ASAP } (\mathrm{G}(\mathrm{V},\mathrm{E})) \ \{ \\ \text{foreach } v_i \text{ in topological order} \\ \text{ schedule } t_i^S \text{ to max } (t_j^S + delay_j) \text{ where } \mathrm{j:}(v_j,v_i) \in \mathrm{E} \\ \text{return}(t^S); \\ \} \\ \\ \text{ALAP } (\mathrm{G}(\mathrm{V},\mathrm{E}),\kappa) \ \{ \\ \text{Schedule } v_n \text{ by setting } t_n^S = \kappa \\ \text{foreach } v_i \text{ in reverse topological order} \\ \text{ schedule } t_i^L \text{ to min } (t_j^L - delay_i) \text{ where } \mathrm{j:}(v_i,v_j) \in \mathrm{E} \\ \} \end{array}

```

Figure 3.3. As-soon-as-possible and as-late-as-possible algorithms.

is determined when the latency bound of ALAP scheduling is set to that given by the ASAP algorithm. Then, taking the difference between scheduled operations according to ASAP and ALAP, each operation that has zero mobility is on the critical path of the system.

### 3.2.4 Force-Directed Scheduling

Another method used for discrete time based methods is Force-Directed Scheduling [36]. This method attempts to balance the concurrency of operations assigned to functional units. To do this, a concept of force is developed for each resource. One common analogy is to view the force of each operation as a spring. Then, a dataflow graph can be viewed as a set of springs pushing against their successors and predecessors. Additional forces to account for the sharing of functional units is also taken into consideration. With this model, a state of equilibrium is found between the forces. When this occurs, the concurrency of operations assigned to functional units gives the sharing of resources. An example of a schedule for the differential equation solver using this method is shown in Figure 3.4. Using this method, only two multipliers and two ALUs are required to complete the system in four time steps. This is an improvement over the ASAP method which requires four multipliers, and the ALAP method which requires three ALUs to complete in the same amount of time. Later, our results are compared against the FDS algorithm, and a similiar method called Force-Directed List Scheduling (FDLS) [36].

Figure 3.4. Force-directed scheduling.

## 3.2.5 Statistical Delay Calculation

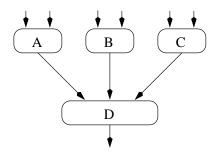

It is critical that accurate estimates be used for asynchronous scheduling in order to achieve optimal scheduling and resource sharing. The delay of a system is more accurately calculated by using the statistical analysis approach presented in [9]. This method models operations with a probability distribution representing the likelihood of completion after a given amount of time. To illustrate, consider the example in Figure 3.5. In this case, operation D cannot begin its computation until all three of its incoming operands A, B, and C are available. An approach that simply finds the starting time of D by taking the maximum completion delay of A, B, and C is shown in [9] to potentially underestimate

Figure 3.5. A data flow graph with four operations: A, B, C and D.

the performance of the system by as much as 21%. This is because worst-case timing analysis only calculates a pessimistic delay.

The statistical delay method is more accurate than these methods. It first calculates the uncertainty of the start time for the system by using delay distributions of operations A, B, and C. In this example, it is assumed that the completion times are normally distributed. The resulting distribution represents the window of time in which an operation may start its calculation. For any time t, assuming statistical independence on each of the inputs A through C, the distribution of D can be calculated. For the probability density function of A, the notation  $f_A$  is used. So, the probability that operation A has completed by time t is:

$$P(A_f \le t) = F_A(t) = \int_0^t f_A(t)dt$$

This means the probability that D can *start* its computation at time t is:

$$P(D_s \le t) = P(A_f \le t) \cdot P(B_f \le t) \cdot P(C_f \le t)$$

By substituting the first equation into the second for A, B and C and taking the derivative of both sides, the start time distribution for D is:

$$f_D(t) = F_A(t) \cdot F_B(t) \cdot f_C(t) + F_B(t) \cdot F_C(t) \cdot f_A(t) + F_A(t) \cdot F_C(t) \cdot f_B(t)$$

Finally, to find the distribution of time for which the operation D is finished, the start time distribution of D is convolved with its computational delay distribution. The ending time distribution is then propagated in a like manner to D's succeeding operations. Using this model the data flow graph can be analyzed and a timing model can be generated.

It is clear that asynchronous scheduling using this method is more accurate but is a computationally expensive task. The shortcoming of this method is that the assumption of independence between signals is not always valid. Systems that have diverging signals from a common source operation that then reconverge at a later point in the data flow graph should, in theory, exhibit some dependence. This means that the assumption of independence in this method could lead to erroneous calculations.

### 3.2.6 Monte-Carlo Delay Calculation

Another method for computing the delay of the system is Monte-Carlo. The Monte-Carlo technique simulates the system until the overall delay of the system converges to a specific time. Since in this method the delay of the system is calculated using Gaussian random variables to model the delays of each operation, Monte-Carlo yields the typical delay of the system.

The advantage of the Monte-Carlo method is that it takes into account signal dependencies. The drawback of the Monte-Carlo method is the large processing time required for convergence, making this type of delay estimation unsuitable during synthesis.

A couple of observations are in order at this point. First, the ASAP and ALAP scheduling techniques are suitable for calculating the conservative schedules for a system. From these schedules, the window of time in which an operation starts and completes can be found, albeit conservatively. Using the ASAP and ALAP schedules, it can be determined which resources are, or are not, in conflict and then share them appropriately. The ASAP and ALAP method cannot determine exactly when, in the typical case, an operation starts and completes. When a more accurate technique is required, the Monte-Carlo method can be used.

# 3.3 Typical Delay

Although very elusive, it is important to have some notion of the typical delay of a system, because in an asynchronous design, minimizing the typical delay is the primary objective when trying to reduce the overall latency. The worst-case, or even best-case, completion delays of two designs can be equal, but each can have different typical delays. Analyzing a design does not require knowing the typical system delay, it only requires knowing, with some degree of accuracy, if the typical delay is better or worse than a competing design.

It was originally thought that as operations are serialized to enable resource sharing the values of the worst-case delay and typical delay of the system would increase together. This would allow us to simply use the worst-case delay of the system as an indicator of the typical delay. Using this method, it seems logical that if a design had a larger worst-case delay, it would then also have a larger typical delay. This, however, is not the case, because it is possible for the worst-case delay of the system to increase, while the typical delay of the system actually decreases.

Using the differential equation solver, from Figure 2.1, the worst-case delay of the system was compared with the Monte-Carlo typical delay of the system. For the addition, subtraction, and comparison operations (ALU operations), delays of two, five, and eight

are used. These correspond to the minimum, typical, and maximum delay of each operation. For all other operations, delays of four, five, and six are used. Note that for this example, all operations in the data flow graph have the same typical delay. Only the best-case and worst-case delays vary. Exploration is then done on the system to find all configurations of the system. It was discovered, that as operations in the graph were serialized that the typical delay of the system did not track the worst case delay of the system. While the worst case delay of the system monotonically increased, the typical delay increased as expected, but it also decreased with certain configurations.

Further analysis of the differential equation solver example showed that this occurs because each ALU on the critical path improves the typical delay by three units. When other operations are on the critical path, they only improve the typical delay by one unit. In other words, it is better for the critical path to be composed with ALUs in place of other operations, because while the worst-case delay may increase, the typical delay is better. This illustrates that the typical delay of the system does not always track the worst-case delay of the system.

## **3.4 Resource Allocation**

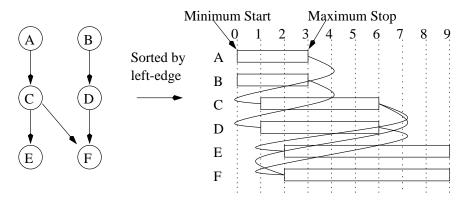

Resource sharing is used to minimize the area required for a design. This is done by determining which operations are scheduled to a particular instance of a resource. An optimum resource sharing is one that minimizes the number of required resource instances. Two or more operations can share the same resource if they are of the same type and they are not in conflict with each other. Operations are in conflict if their execution windows overlap in time. This happens when either operation starts before the other has completed. Operations that are scheduled in disjoint windows of time are guaranteed not to overlap and are, therefore, always compatible. The conflict window is determined by using the best-case ASAP schedule to determine the start time of the window and the worst-case ALAP schedule to determine the stop time of the window.

Another way to show that two operations are compatible is to analyze the data flow graph. If there is a path from operation i to operation j, then those two operations are compatible regardless of their scheduled windows of time. This is because the existence of a path guarantees that operation i must complete before operation j begins. The more edges present in a graph, the more sharing that can potentially occur. Edges used to explicitly denote two sharable operations are known as *resource edges* and are added to the data flow graph during exploration. They are distinguished from *data edges*, because they do not imply the transfer of data from one operation to the next. Resource edges enforce that the two operations occur at disjoint times and denote the ordering in which operations must occur.

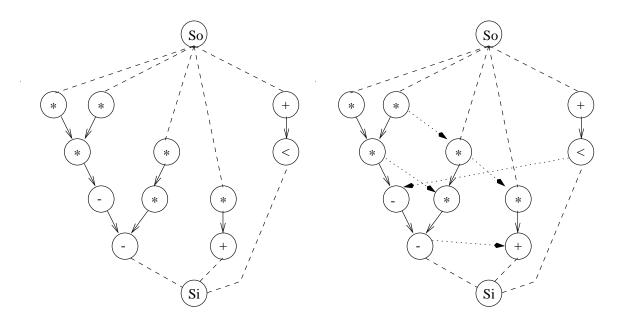

Figure 3.6 shows a data flow graph with only data edges. In this configuration, four multipliers are required and three ALUs. With resource edges, only two multipliers and one ALU are required. Granted, however, in this case, the overall delay of the system may not be equal. Note that there are many ways to add resource edges to the graph. Each resource edge added to the graph, in essence covers an aggregate of all the possible discrete time schedules that the given operation sequencing and resource sharing would produce. Hence, scheduling of operations is done independent of the discretization of time. For efficiency, Mercury utilizes both the information from the data flow graph and where applicable, conservative scheduling information to perform resource sharing.

This approach is beneficial for asynchronous design because the computational complexity is constant with regard to the discretization of time. Using resource edges, in effect, allows scheduling to take on a continuous time paradigm. Our tests showed that synchronous methods, such as Force-Directed Scheduling, become computationally

Figure 3.6. Data flow graphs without and with resource edges.

infeasible as the granularity of time is increased. Figure 3.7 illustrates the crossover in the usefulness of the two methods. Being able to discretize time without a loss in performance is important for asynchronous design because of the naturally continuous nature of events which can occur in an asynchronous circuit.

## 3.4.1 Left-Edge Algorithm

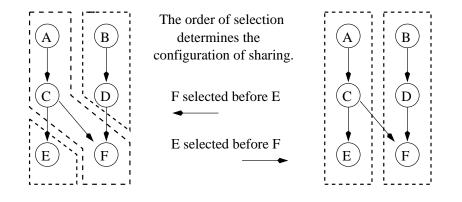

Using the left-edge algorithm from [26], it is possible to do resource sharing. The algorithm first sorts the operations or nodes by their scheduled start time, or *left-edge*. It considers one instance of a resource at a time and assigns as many operations as possible to that instance by searching the nodes sorted in ascending order. Each iteration of the algorithm considers a new instance of the resource, until all operations are allocated to a specific resource instance.